# Project Report ATC-87, III

# The Aircraft Reply and Interference Environment Simulator (ARIES) Volume 3: Programmer's Manual

M. Goon D. A. Spencer

22 March 1979

# **Lincoln Laboratory**

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Lexington, Massachusetts

Prepared for the Federal Aviation Administration, Washington, D.C. 20591

This document is available to the public through the National Technical Information Service, Springfield, VA 22161 This document is disseminated under the sponsorship of the Department of Transportation in the interest of information exchange. The United States Government assumes no liability for its contents or use thereof.

| •                                                                                              |                                                                                                                                                                                                   |                                                                                                                                                                                                                     | recharteas Report                                                                                       | . Documenta cron ragi                                                      |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 1. Report No.                                                                                  | 2. Government Acce                                                                                                                                                                                | ssion No. 3. F                                                                                                                                                                                                      | Recipient's Catalog                                                                                     | No                                                                         |

| ₩ FAA-RD-78-96                                                                                 |                                                                                                                                                                                                   |                                                                                                                                                                                                                     |                                                                                                         | j                                                                          |

| 4. Title and Subtitle                                                                          |                                                                                                                                                                                                   | 5. F                                                                                                                                                                                                                | Report Date                                                                                             |                                                                            |

|                                                                                                | The Aircraft Reply and Interference Environment Simulat                                                                                                                                           |                                                                                                                                                                                                                     | 22 March 1979                                                                                           |                                                                            |

| Volume 3: Programmer's Manual                                                                  |                                                                                                                                                                                                   | ) 6. F                                                                                                                                                                                                              | Performing Organizat                                                                                    | ion Code                                                                   |

| 7. Author(s)                                                                                   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                             | 8. P                                                                                                                                                                                                                | erforming Organizat                                                                                     | ion Report No.                                                             |

| Mîchael Goon and David A. Spencer                                                              |                                                                                                                                                                                                   |                                                                                                                                                                                                                     | ATC-87, Volum                                                                                           | ne 3 = ==                                                                  |

| 9. Performing Organization Name and Address                                                    |                                                                                                                                                                                                   | 10.                                                                                                                                                                                                                 | Work Unit No.                                                                                           |                                                                            |

| Massachusetts Institute of Technology                                                          |                                                                                                                                                                                                   |                                                                                                                                                                                                                     | Proj. No. 052-2                                                                                         | 241-04                                                                     |

| Lincoln Laboratory                                                                             |                                                                                                                                                                                                   | 11.                                                                                                                                                                                                                 | Contract or Grant N                                                                                     |                                                                            |

| Lexington, MA 02173                                                                            | P.O. Box 73<br>Lexington, MA 02173                                                                                                                                                                |                                                                                                                                                                                                                     | DOT-FA77-WA                                                                                             |                                                                            |

| 12. Sponsoring Agency Name and Address                                                         |                                                                                                                                                                                                   | 13.                                                                                                                                                                                                                 | ype of Kepart and                                                                                       | Period Covered                                                             |

| Department of Transportation                                                                   |                                                                                                                                                                                                   | :::                                                                                                                                                                                                                 | Project Report                                                                                          |                                                                            |

| Federal Aviation Administration Systems Research and Development                               | Comples                                                                                                                                                                                           |                                                                                                                                                                                                                     |                                                                                                         |                                                                            |

| Washington, DC 20591                                                                           | bervice                                                                                                                                                                                           | 14;                                                                                                                                                                                                                 | Sponsoring Agency (                                                                                     | Code                                                                       |

|                                                                                                |                                                                                                                                                                                                   |                                                                                                                                                                                                                     |                                                                                                         |                                                                            |

| 15. Supplementary Notes                                                                        |                                                                                                                                                                                                   | 7 ! ! 7 -1                                                                                                                                                                                                          |                                                                                                         |                                                                            |

| The work reported in this document<br>Massachusetts Institute of Technolo<br>F19628-78-C-0002. |                                                                                                                                                                                                   |                                                                                                                                                                                                                     |                                                                                                         |                                                                            |

| 16. Abstract                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                     |                                                                                                         |                                                                            |

| Volume 2: App                                                                                  | Beacon System (Dataped traffic model to documentation for aciples of Operation endices to the Pringrammer's Manual mual describes the ces controlled by the trace boards that a computer. The log | ABS) sensor under its speci- to generate simulated airc ARIES, of which this is the ciples of Operation operation, signal formats are Eclipse computer. The reside in the computer cha gic of the devices themselve | ified maximum ai craft replies and he third volume, and protocols of descriptions are ssis and the form | rcraft load, fruit, feeding consists of: the Lincoln primarily lats of the |

|                                                                                                |                                                                                                                                                                                                   |                                                                                                                                                                                                                     |                                                                                                         |                                                                            |

| 17. Key Words                                                                                  | (DARC)                                                                                                                                                                                            | 18. Distribution Statement                                                                                                                                                                                          |                                                                                                         |                                                                            |

| Discrete Address Beacon System<br>ARIES                                                        | r (DVR2)                                                                                                                                                                                          | Document is available to the public through                                                                                                                                                                         |                                                                                                         |                                                                            |

| Fruit generation                                                                               |                                                                                                                                                                                                   | the National Technical Information Service,                                                                                                                                                                         |                                                                                                         |                                                                            |

| Simulation<br>Air traffic models                                                               |                                                                                                                                                                                                   | Springfield, Virg                                                                                                                                                                                                   | ginia 22151.                                                                                            |                                                                            |

| Secondary radar                                                                                | !                                                                                                                                                                                                 |                                                                                                                                                                                                                     |                                                                                                         |                                                                            |

| 19. Security Classif. (of this report)                                                         | 20. Security Class                                                                                                                                                                                | iif. (of this page)                                                                                                                                                                                                 | 21. No. of Pages                                                                                        |                                                                            |

| Unclassified                                                                                   | Unclass                                                                                                                                                                                           |                                                                                                                                                                                                                     | 64                                                                                                      | ]                                                                          |

# TABLE OF CONTENTS

|       |                                         | Page   |

|-------|-----------------------------------------|--------|

| 1.0   | INTRODUCTION                            | 1      |

|       | 1.1 Purpose                             | 1<br>1 |

| 2.0   | RECEIVER                                | 4      |

| 3.0   | CONTROLLED REPLY GENERATOR              | 7      |

| 4.0   | FRUIT REPLY GENERATOR                   | 12     |

| 5.0   | SELF TEST UNIT                          | 17     |

| 6.0   | RADAR REPORT INTERFACE                  | 20     |

| 7.0   | STATUS FORMATTER                        | 21     |

| 8.0   | UNIVERSAL INTERVAL TIMER                | 23     |

| 9.0   | RANDOM NUMBER GENERATOR                 | 26     |

| REFE  | RENCES                                  | 27     |

| APPEI | NDIX: DEVICE SUMMARIES AND DATA FORMATS | A-1    |

# LIST OF ILLUSTRATIONS

| 1.1 | ARIES Block Diagram                              | 2  |

|-----|--------------------------------------------------|----|

| 3.1 | Controlled reply generator components            | 8  |

| 3.2 | Block diagram of the CRG interface               | 10 |

| 4.1 | Fruit reply generator components                 | 13 |

| 4.2 | Block diagram of fruit reply generator interface | 14 |

| 8.1 | Major UIT registers                              | 24 |

#### 1.0 INTRODUCTION

#### 1.1 Purpose

The Aircraft Reply and Interference Environment Simulator (ARIES) is a test system designed to simulate a high density radar beacon environment for the purpose of evaluating Discrete Address Beacon System (DABS) sensors. DABS is an improved surveillance and communication system designed to support the needs of the civil air traffic control system. For a more complete description of both the DABS system and ARIES, please see Volume 1 of this document. It is recommended that the overview sections of that volume be read before reading this manual, in order to give the correct context to the material presented here.

This manual describes Lincoln Laboratory-built input/output devices used in the ARIES system from the point of view of persons trying to control these devices from the computer. The descriptions are primarily concerned with the logic of the interface boards that reside in the computer chassis and the formats of the words transferred to and from the computer. The logic of the devices themselves is described only to the extent necessary to understand the interface protocols and data formats.

Devices not built by Lincoln Laboratory are described in separate manuals provided by their manufacturers (see the list of references).

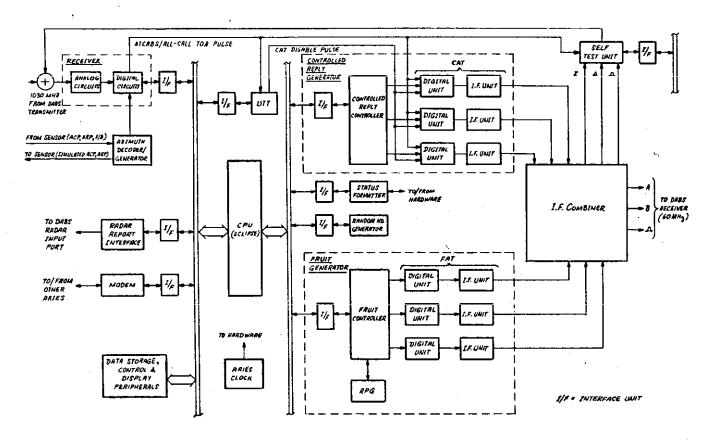

Figure 1.1 shows the overall block diagram of the ARIES System, and all interfaces to the DABS sensor.

### 1.2 Data General I/O Interface Conventions

ARIES employs a Data General 'Eclipse' computer and associated I/O devices and interfaces. Data General interfaces have two modes of data transfer. One is programmed I/O, where the transfer of each word is controlled by the software. The other is data channel I/O, where the software merely specifies to the device the address and length of a buffer area in memory (via programmed I/O). All transfers to or from that buffer are controlled by the device interface, independently of the software.

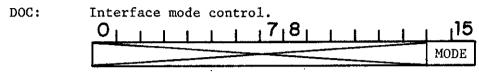

Programmed I/O is conducted between a CPU register and one of three "registers" on the device interface, the A, B, and C registers. These may or may not be implemented as unique hardware registers. It is better to regard A, B, and C as device addresses of particular components of the interface, rather than as actual registers. Output to these registers occurs via the DOA, DOB, and DOC instructions, respectively. The corresponding input instructions are DIA, DIB, DIC.

Fig.1.1. ARIES Block Diagram.

Each device interface has three status flip-flops which are controlled by the software, the BUSY, DONE, and INTERRUPT DISABLE flip-flops. If BUSY is set, the device is active. DONE is always zero in that circumstance. When the device completes its operation, it clears BUSY and sets DONE. This automatically causes an interrupt to be generated at the CPU, unless the INTERRUPT DISABLE flip-flop is set, in which case the interrupt will be inhibited until INTERRUPT DISABLE is cleared. If DONE is set when INTERRUPT DISABLE is zero, an interrupt will be generated immediately. A device is completely inactive when both BUSY and DONE are zero.

There are several signals available to control these status flip-flops. The START line, when pulsed, will set BUSY and clear DONE. This usually has the effect of activating the device. The CLEAR line, when pulsed, will set both of these to zero. The IORST line is similar to CLEAR, except that the INTERRUPT DISABLE flip-flop is also cleared.

To pulse the START and CLEAR lines the letters S and C respectively are appended to the programmed I/O instruction mnemonics (e.g., DOAS, DIBC), or to a NO I/O TRANSFER instruction (NIOS, NIOC). There is a third control line, called the P line, which is operated similarly by appending a P to the I/O commands. It has no standard usage, and is interpreted differently by each device.

The IORST line is pulsed by the I/O RESET instruction, or by toggling the RESET switch on the front panel. It is pulsed automatically by the CPU when power is first turned on. Note that the input and output instructions, and any START, CLEAR, or P pulse associated with them, affect only the addressed device, while an IORST affects all devices.

INTERRUPT DISABLE is normally set and cleared by a MASK OUT instruction. This instruction places the contents of a specified CPU register on the data lines, and then sends a special control pulse. Each device looks at only one of the 16 data bits, and loads the value of that bit into its INTERRUPT DISABLE flip-flop on receipt of the pulse.

For more information on the operation of the Data General I/O system, please see the Data General documentation in the references.

#### 2.0 RECEIVER

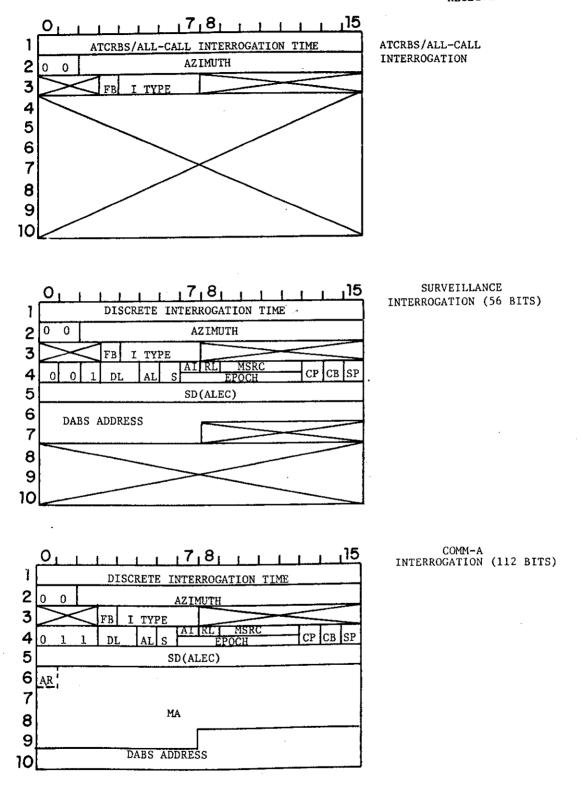

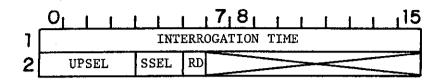

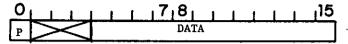

The ARIES receiver consists of an analog section and a digital section. The analog section receives its input from the ARIES RF port of the DABS sensor at 1030 MHz and demodulates it, providing output levels compatible with digital logic. The digital section detects arriving interrogations, determines their mode, and in the case of discrete interrogations it assembles the data bits and removes the error detection encoding from the DABS address field. At each interrogation, an interrupt is generated to inform the computer of its arrival and a 10 word interrogation data block is created in a buffer area in the computer's memory. This block contains the time of arrival, the antenna boresight azimuth at arrival, the mode, and (for discrete interrogations only) the data bits. The format is shown in the Appendix.

The receiver uses a data channel interface to store interrogation blocks directly into the memory. Therefore, it can operate independently of the computer once an input buffer area is specified to it. A 640 word buffer is required, allowing 64 ten word interrogation blocks to be stored. The interface maintains a count of the number of interrogation blocks that have been completed. This can be read by the software to determine how many complete interrogation blocks are awaiting processing. The software can also decrement this counter once it has completely processed an interrogation.

The input buffer is treated as a circular buffer by the interface. As long as the interrogation counter does not overflow (as it will if there are 64 unprocessed interrogations) the interface will continue storing interrogation blocks. If it reaches the end of the buffer area, it will continue at the beginning of the buffer.

The interrupt generated with each interrogation occurs at the time of bracket detection for ATCRBS or ATCRBS/All-Call interrogations, and at the time of sync phase reversal detection for discrete interrogations. In the case of discrete interrogations an additional 14 to 28 µsec can elapse before the last word of the interrogation block is stored, depending on whether the interrogation is a surveillance or Comm-A interrogation respectively. Therefore, it should not be assumed that occurrance of an interrupt means that the data is available. The interrogation counter must be tested to determine if the data block is complete, as it will only be incremented upon storage of the 10th word of the block.

The interrupt logic for this interface is a modification of the Data General standard. Two DONE flip-flops are used to indicate different conditions. The standard DONE, which is tested by the I/O SKIP instruction, is set only upon interrogation counter overflow. As in the Data General standard, the BUSY flip-flop is simultaneously reset, disabling the interface. This occurrence should be treated as an error condition.

The second DONE flip-flop cannot be tested by the I/O SKIP, but does cause an interrupt to be generated. The BUSY flip-flop is not reset. This is used to indicate the arrival of an interrogation. When either of the DONE flip-flops is set, an interrupt is generated, and the INTA instruction will indicate that the interrupt is from the receiver. The I/O SKIP instruction can be used to distinguish the two cases by testing the standard DONE flip-flop.

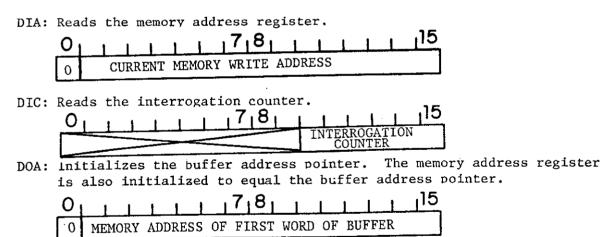

The interface must be initialized by sending a CLEAR or IORST pulse to assure that BUSY and both DONE flip-flops are reset, and that the interrogation counter is zeroed. Then the address of the origin of the buffer area must be set via a DOA instruction. The buffer length is always assumed to be 640 words. Sending a START pulse will then activate the receiver.

Upon receipt of an interrupt from the receiver, the program must first check whether the interrupt indicates buffer overflow or the arrival of an interrogation. If the latter, it must first reset the second DONE flip-flop by means of the P pulse. Then it must repeatedly read the interrogation counter via a DIC instruction until a non-zero count is indicated. It can then process the interrogation.

In order to be able to locate the interrogation, the software must maintain a buffer pointer of its own. It is <u>not</u> correct to read the receiver's memory address register for this purpose. Every time BUSY is set, the interface's memory address register is set to the beginning of the buffer, and the first interrogation will appear there. Subsequent interrogations will appear in successive locations until the end of the buffer is reached (at the end of every 64th interrogation) at which time the address register will be set back to the beginning of the buffer.

When the program has completed processing the interrogation, it must decrement the interrogation counter via a DOC instruction. This DOC does not transmit any data, but merely provides a pulse to the interface which is used to decrement the count.

In processing interrogations, the programmer should note that the interrogation time field has different precision for DABS and ATCRBS/All-Call interrogations. The receiver has a 20 bit range counter that counts at a 16 MHz rate. The DABS interrogation time is used to calculate the precise reply time and therefore the low order 16 bits of this counter are used. This allows a maximum unambiguous round trip time of 4.096 msec. The ATCRBS/All-Call time is only used in obtaining the inter-interrogation times while ARIES is finding the interrogation pattern of the DABS sensor. Less precision and a longer unambiguous interval is required, and so the high order 16 bits of the 20 bit counter are returned as the ATCRBS/All-Call interrogation time.

Before exiting the interrogation interrupt routine, it is worth checking the interrogation count to determine if any more interrogations have arrived during the processing interval. Processing these immediately will avoid the overhead of saving and restoring the machine state for each interrupt.

The current value of the receiver's memory address register can be read via a DIA instruction. This is useful primarily for diagnostic purposes, and points to the next location to be written into by the interface.

Note that, since the interrogation interrupts do not reset the BUSY flip-flop, the receiver will run continuously once started. It will be disabled only by an I/O RESET instruction (or a reset from the front panel), a CLEAR pulse, or a buffer overflow condition.

#### 3.0 CONTROLLED REPLY GENERATOR

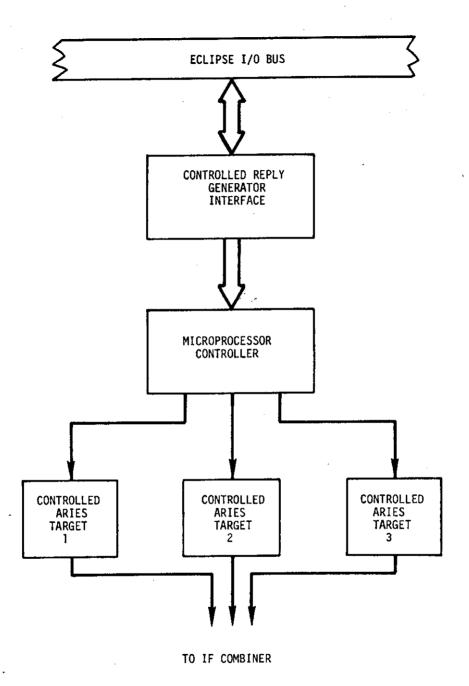

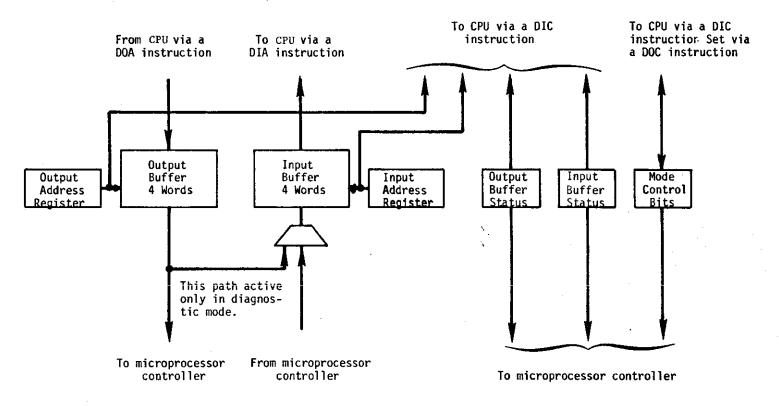

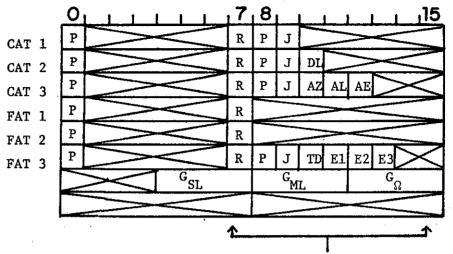

The Controlled Reply Generator (CRG) generates both DABS and ATCRBS replies under software control. All non-fruit replies are generated by this portion of ARIES. As shown in Fig. 3.1 the CRG consists of several components. The program creates reply data and transmits it to buffers in the interface. The microprocessor controller polls the Controlled ARIES Targets (CATs) to see if any are ready for new reply data. When new data can be accepted by a CAT, the controller obtains the next set of reply data from the interface buffers, if any is available, and places it into the CAT.

All programming for the CRG involves only the interface circuits, and the rest of this discussion focuses exclusively on the operation of the interface. The interface serves a dual purpose. First, it forms a link between the computer and the controller. Second, it provides a buffer space where the program can place replies as they are generated. The advantage of having replies stored in the interface rather than in the computer's memory is that the data transfer rate to the controller is increased. This makes it possible to handle bursts of replies that would not be transferred in time if the Data General direct memory access channel was used to obtain the data from the computer's memory. It also reduces the amount of interference between central processor and I/O memory access requests.

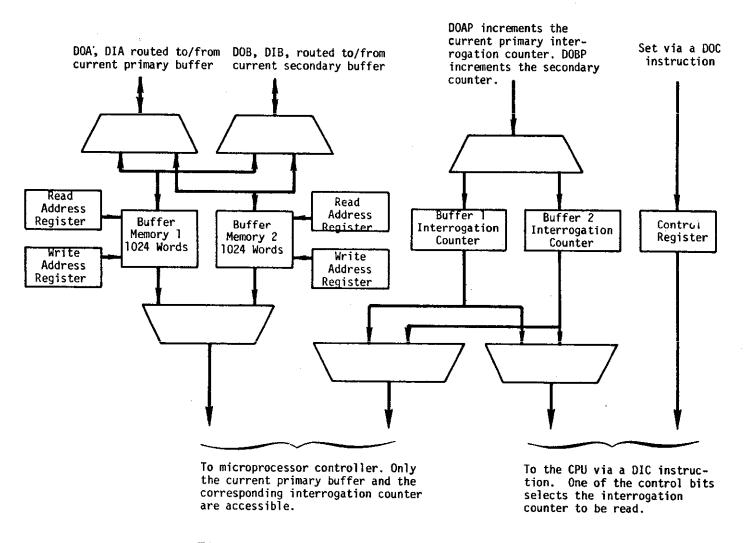

Two buffer memories are built into the interface. At any time, one is labeled as primary and the other as secondary, but the roles can be reversed under program control. Each buffer is 1024 words long (16 bit words). This allows the storage of 102 DABS discrete or all-call replies (10 words each) or 256 ATCRBS replies (4 words each). The microprocessor controller can read reply data only from the buffer designated as primary.

To understand the functioning of the primary and secondary buffers, it is necessary to understand how ARIES handles discrete and ATCRBS/All-Call interrogations. Discrete interrogations are handled as they are received. The ARIES receiver interrupts the computer, which then processes the interrogation data and generates a reply, which is immediately sent to the CRG. This can be done because the DABS transponder turn-around time of 128  $\mu sec$  allows sufficient processing time.

In the case of ATCRBS interrogations, however, the specified turn-around time is 3 µsec. This does not allow sufficient time for the software to process these interrogations "in real time". Fortunately, the time and mode of ATCRBS/All-Call interrogations is predictable, as the sensor follows a fixed interrogation pattern. Therefore, the ARIES system can prepare the complete set of ATCRBS and all-call replies for a given interrogation in advance of that interrogation actually being sent. When the interrogation is received, these pre-computed replies are transmitted and ARIES begins generating the replies for the next ATCRBS/All-Call interrogation.

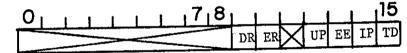

Fig. 3.1. Controlled Reply Generator Components.

The secondary buffer is the storage area for these pre-computed ATCRBS and all-call replies. Since the controller can only read from the primary memory, these will not be transmitted. When the ATCRBS/All-Call interrogation is received, the software switches the buffer status. Since the ATCRBS and All-Call replies are then in the primary buffer the controller immediately begins sending them to the CATs.

DABS discrete replies are to be transmitted immediately, and so the CPU must store them directly into the primary buffer. This introduces the problem that this buffer may be simultaneously read from by the controller and written into by the CPU. Therefore, some control logic is needed so that it is always accurately known how many replies have yet to be read from the buffer. Each buffer therefore has associated with it a reply counter. This is incremented each time a complete reply is entered into the buffer by the software and decremented each time the controller reads a reply. Just as the controller can only look at the primary buffer, it can only access the primary reply counter. Figure 3.2 is a block diagram of the overall interface.

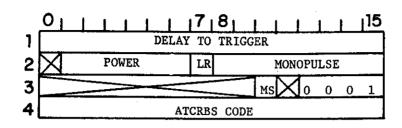

To write a word into the primary memory, the program executes a DOA instruction. Words must be written in the order shown in the Appendix, and are stored at successive locations in the buffer. Similarly, to store a word into the secondary memory, a DOB instruction is executed. To store the last word of a reply (word 4 for ATCRBS, word 10 for DABS All-Call or discrete replies) either a DOAP or DOBP instruction must be used, as this increments the reply counter for the buffer in addition to storing the last reply word. The result of issuing a pulse on the P line other than in conjunction with DOA or DOB is undefined.

The interface buffers are circular buffers. After word 1023 is written, word 0 will be the next to be written. Therefore, if more than 1024 words are written before any reading takes place, some locations will be overwritten. There is no hardware protection against this, nor any error indication. It is the responsibility of the software to keep track of the available memory. The size of the buffers is such, however, that they should never be more than 50% to 60% full.

It is acceptable to start a reply at the end of the buffer and finish it at the beginning, or in other words to split it between the end and beginning of the buffer.

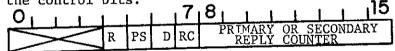

The DOC instruction is used to control the interface operations. As shown in the Appendix, bits are provided to specify which buffer is primary, to select whether the primary or secondary reply counter is to be read by the next DIC instruction, to place the interface in a diagnostic mode, and to reset the microprocessor. The DIC instruction can be used to read back these control bits, as well as the primary or secondary reply counter, for test purposes.

Fig. 3.2. Block Diagram of the CRG Interface.

If the interface is placed in the diagnostic mode, the controller is inhibited from reading either buffer, and the program is allowed to read either buffer by means of DIA or DIB instructions for the primary and secondary buffer respectively. Successive DIAs or DIBs will read successive buffer locations, starting at whatever address the read address register was left indicating when diagnostic mode was entered. After location 1023, location 0 will be returned.

#### 4.0 FRUIT REPLY GENERATOR

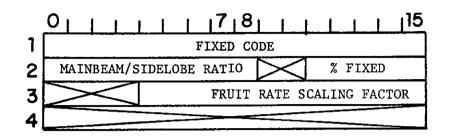

The Fruit Reply Generator (FRG) provides a means of inserting simulated fruit replies into the signal being sent to the sensor. These replies are randomly generated, with exponentially distributed inter-arrival times. The following parameters of the random reply generation process can be controlled by the programmer: average fruit rate, the fraction of replies in the main antenna beam (as opposed to being in the sidelobes), the fraction of replies that will have a fixed known value for their data bits (as opposed to having randomly generated data bits) and the specific fixed data bits to be used. Only ATCRBS replies are generated by the FRG.

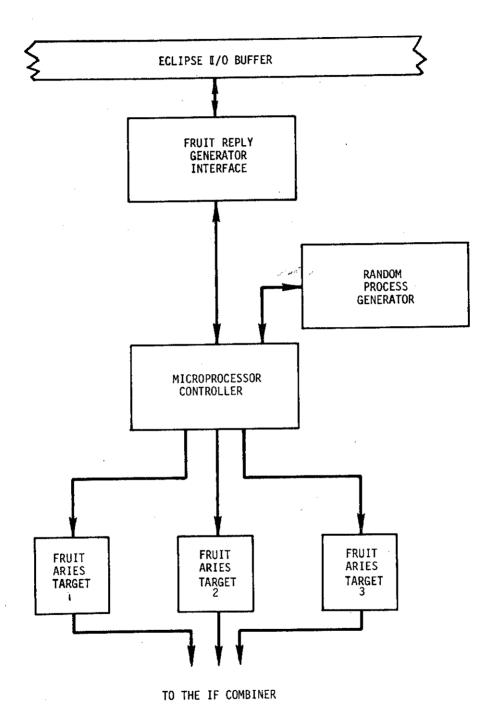

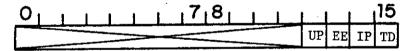

The FRG consists of several components as shown in Fig. 4.1. The microprocessor controller is the central controlling element of the FRG. In normal operation, it polls the three Fruit ARIES Targets (FATs) to find one that can accept another reply block. At that point, it obtains the parameters for a fruit reply from the Random Process Generator (RPG), and sends it to the FAT.

The controller also periodically polls the interface to the computer. By this means it can obtain new fruit parameters from the computer and transmit them to the RPG. There are also diagnostic modes whereby the RPG reply parameters can be sent to the computer, or the reply parameters can be obtained from the computer rather than from the RPG.

Programming for the FRG is concerned primarily with the interaction between the program and the interface, and so the rest of this discussion focuses entirely on the interface.

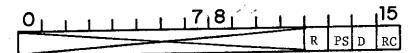

Figure 4.2 is a diagram of the interface. There are two nearly independent channels, one for transferring data from the computer to the controller and the other for transfers in the opposite direction. Each such channel consists of a four word memory, a memory address register, and a bit to indicate whether the memory is in a read or write mode. In addition to the two data transfer channels, there is a two bit control register, which determines whether the FRG is in its normal operating mode or in one of three possible diagnostic modes.

All transfers over the two channels must be in groups of four words. The source of the data (i.e., the program or the controller) first must check the status bit to be sure that it is allowed to write into the memory. It then writes four words into the memory, causing the memory address register to wrap around and be left pointing at the first word stored. The status bit is then switched automatically by the interface, allowing the reader to access the data. When four words have been read, the status bit will switch back to its original state. A status bit value of 0 always means that the computer has access to the memory.

Fig.4.1. Fruit Reply Generator Components.

Fig. 4.2. Block Diagram of Fruit Reply Generator Interface.

Note that both the input and output status bits will change state whenever the memory address for the corresponding buffer wraps around from the last word to the first. The value of the status bit does not interlock the memory to prevent either the microprocessor or the computer from accessing either buffer at any time. Therefore, for example, the program is perfectly free to output 8 successive words. This will cause the output status bit to change value twice, and leave it in its original state.

To send data to the microprocessor, the programmer follows the above protocol using the output channel. The status bits can be obtained by means of the DIC instruction. Data is transferred to the output memory by means of four DOA instructions. The format of the RPG control words and the order in which they are to be sent is shown in the Appendix. Similarly, four DIA instructions are used to read data from the input channel. The input data format is also shown in the Appendix.

Whenever the RPG parameters are changed (by sending 4 words to the controller over the output channel) the RPG is reset to its initial state.

Note that the DIC instruction also reads the current memory address register values for both channels. While only four words of memory are used in each channel, the memories are implemented using locations 4, 5, 6, and 7 of a 16 word memory. Four bits are provided to read the address register, although only the above four values should ever appear.

The mode control bits are set using a DOC instruction, as shown in the Appendix. Four modes are possible, as follows:

| Control Bits | Mode                |  |  |

|--------------|---------------------|--|--|

| 11           | Normal              |  |  |

| 10           | RPG diagnostic      |  |  |

| 01           | FAT diagnostic      |  |  |

| 00           | Interface loop test |  |  |

The normal mode is the usual operational mode of the interface. Only the output channel is used. In running tests with a DABS sensor the ARIES software periodically (every sector of antenna rotation, or 11.25°) writes four words of RPG fruit parameters into the output memory. This data is then taken by the controller and loaded into the RPG. By this means the characteristics of the fruit replies generated by the RPG can be varied from sector to sector.

The RPG diagnostic mode provides a way of checking the RPG operation from the computer. Both the output and the input channels are used. To begin the operation, the program must initialize the RPG with some fruit parameters using the output channel. The controller will then request fruit reply data from the RPG and transfer it to the computer via the input channel. As each

reply is read by the program, a new one will be sent by the controller. This operation continues until enough data is gathered to check RPG operation. Since the random process generator is only pseudo-random, and therefore the sequence of values is repeatable, the received sequence can be compared against the expected sequence. The whole procedure may then be repeated for different fruit parameters to assure that the fruit characteristics change appropriately.

Normally the FATs receive fruit reply information from the RPG via the controller, and generate the appropriate analog reply signal at 60 MHz. To check the operation of the FATs one might consider looking at fruit replies with the ARIES Self Test Unit. However, there are problems with this in that (a) the reply parameters are random, making it difficult to determine if the results are correct and (b) even at low fruit rates replies will occasionally overlap and garble the results of the test.

To avoid these problems the FAT diagnostic mode of the FRG allows the software to insert known reply data into the FATs, bypassing the RPG. Only the output channel is used in this case. The data format is identical to the RPG diagnostic input data format, shown in the Appendix. The replies generated can then be observed using the Self Test Unit, without fear of garbled data.

All the above tests are meaningless if the interface itself is not working properly. To check this link between the computer and the microprocessor controller, the interface loop test mode is provided. This cascades the output memory and the input memory such that any data written into the output memory will be read from that memory and written into the input memory. A diagnostic program can verify the correct operation of both these memories by writing four words into the output channel, reading four words from the input channel, and verifying that they match.

The interface generates an interrupt only upon an error condition. If a FAT fails to request new data within 5 msec of the last time data was sent to it, it is considered to have failed and the controller will signal the interface to cause an interrupt. The BUSY bit must of course be set if this interrupt is to be seen.

#### 5.0 SELF TEST UNIT

The purpose of the ARIES Self Test Unit (STU) is to allow for complete loop checks of most of the Lincoln Laboratory built equipment in ARIES, especially the analog equipment such as the receiver, the target generators, and the IF combiner. These tests can be conducted completely independently of the DABS sensor under test, and provide a means of verifying the correct operation of ARIES before any such test.

The STU is composed of two independent sections. The first of these is capable of generating a variety of interrogations at 1030 MHz which are entered into the receiver's input port. The typical mode of operation is for a program to specify a particular interrogation to be generated and to then look at the resulting input data block from the receiver and compare it against the expected result. This provides a complete loop check of the receiver, both the analog and digital portions.

The second section receives as inputs the  $\Sigma$ ,  $\Delta$ , and  $\Omega$  signals from the IF combiner. One of these signals can be selected by the program as the signal to be sampled. When a reply is detected an amplitude sample is taken by an A/D converter and the data bits are also sampled. The program can then read the time of arrival, the amplitude, and the data bits. To perform a complete loop check of the reply generator circuitry, the diagnostic program must generate a series of replies. These should cover the entire range of amplitudes and off-boresight angles, all reply modes, and a variety of data content. The resulting signals are then sampled using the STU, and compared against the expected results.

The operation of both sections of the STU is controlled by two control registers. These can be altered under program control by executing two successive DOA instructions. Both words must be changed if either is to be changed. The STU will interpret every odd numbered DOA as a new transmission of control word 1. The control words remain in effect until two other words are sent. The format of these words is shown in the Appendix.

To generate a test interrogation, the program must specify an interrogation time and an interrogation type (one of up to 15 pre-stored interrogations, not all of which are currently implemented). Once the two control words containing this information have been transferred, the specified interrogation will be sent every time the STU clock equals the specified interrogation time. Since the STU clock is 16 bits wide, driven at 16 MHz, an interrogation will occur every 4.096 msec. If multiple interrogations are not desired, the program must disable the STU after receipt of the first interrogation by executing an NIOC instruction. The BUSY/DONE logic is not used for interrogation generation.

To listen to replies, the program must specify whether the  $\Sigma$ ,  $\Delta$ , or  $\Omega$  channel is to be sampled, and whether the reply mode will be ATCRBS or DABS. Normally the interrogation generator should be turned off by zeroing the interrogation type field. Once the two control words have been transferred containing this information, a START pulse must be issued. At that point the STU begins looking for a reply. Next the program must cause a reply of the desired type to be generated via the Controlled Reply Generator or Fruit Reply Generator. When the STU has completely received this reply BUSY will be cleared, DONE will be set, and an interrupt generated.

At this point 11 words of information are available from the STU. The data includes the time of arrival, the amplitude, an indication of whether the reply was left or right of boresight (this is valid only when the  $\Sigma$  and  $\Delta$  amplitudes are equal and near their maximum level), the data bits, an error bit which is set if the pulse position modulation (PPM) format of a DABS reply appears incorrect, and a copy of the STU control bits to verify that the appropriate data was sampled. The format of this data is shown in the Appendix.

To obtain this data the programmer executes successive DIA instructions. The words are returned in the order shown in the Appendix. It is not necessary to read all 11 words, or to read any of them. Issuing a START pulse will reset the STU and it will begin looking for another reply using the previous control words. Alternatively, the control words can be changed and a START pulse issued.

It is possible to set the STU up to simultaneously send an interrogation and listen for a reply. This could be useful in performing a complete check of the interrogation processing and reply generator portions of the system, including the real time software which receives the interrogation and generates the reply. Care must be exercised, however, to be sure that a START pulse is not sent in the middle of a reply, as this will result in a garbled input. The reply processing portion of the Self Test Unit does not check for preambles, or bracket pulses, but instead will start sampling reply data when triggered by the first pulse leading edge sensed after the START pulse is received.

It is also possible to listen to replies from the Fruit Reply Generator using the STU. This has diagnostic value in testing that the various IF signals are generated properly by that unit. However, the STU can only process one reply at a time, and overlapping fruit replies will give anomalous results. Therefore, the fruit generation must be controlled directly by the program, bypassing the hardware Random Process Generator (this is possible by means of one of the diagnostic modes of the Fruit Reply Generator).

It is sometimes useful in running tests to know approximately what value the ARIES range clock has. One way of controlling this is to send an ATCRBS

interrogation, which forces all the system range clocks to zero, including those of the receiver, Controlled Reply Generators, and the STU. Alternatively, sending a DABS interrogation will cause the receiver clock to be read and inserted into the interrogation data, providing the program with the current clock value.

# 6.0 RADAR REPORT INTERFACE

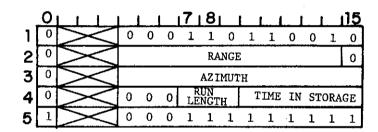

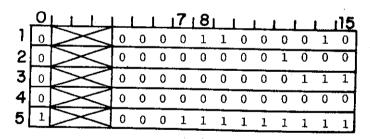

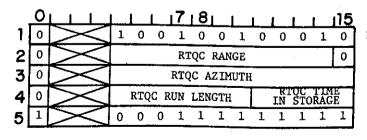

The purpose of this device is to generate radar target reports in Production Common Digitizer (PCD) format for serial transmission to the radar input port of the DABS sensor. It is a data channel device, and therefore can independently transmit an entire buffer of reports once initialized by the software.

To initialize the transmission, a DOA instruction is used to pass the address of the first word of the buffer and a DOB instruction is used to pass the two's complement of the word count. A START pulse will then begin the transmission. The DONE flip-flop will be set and an interrupt generated when the buffer transmission is completed. A DIA instruction can be used to read the current contents of the interface's memory address register.

Each word in the data buffer represents 12 bits of data, stored in bits 4-15. Bit 4 is transmitted first. Bit 0 controls whether even or odd parity will be generated by the interface for those bits (0 is odd, 1 is even parity). Including parity, 13 bits are serially transmitted to the sensor for each word taken from memory. Bits 1-3 of a memory word are ignored.

A surveillance report consists of 4 words, or 48 data bits, or 52 bits including parity. The format is shown in the Appendix. These words all must have odd parity. Reports, in turn, must be separated by at least one idle character. The data bits for this idle character are 000 111 111 111 with even parity. It is recommended that this idle character be considered the first or last word of each report, for a total of 5 words per report.

When no data is being transmitted, the interface continually sends idle characters over the serial link.

#### 7.0 STATUS FORMATTER

This device is used to read various manual switch settings on the ARIES devices, and also receives error signals and status lines from several ARIES devices. In the normal mode of operation it sequentially polls devices for their current status. The new value of a device's status is compared against the old value. If they are not equal, polling is stopped at the end of the current polling cycle and an interrupt is generated to inform the computer.

There are two conditions under which an interrupt will not be generated. If the only bit that has changed is the low order bit of the 8 bits of status for some device, no interrupt will be generated. This bit is used only as a status indicator bit, never an error bit. The second condition which will inhibit interrupts is if the programmer has set the ERROR ENABLE bit (EE) in the status formatter control register to zero. This differs from simply masking the interrupt by means of the MSKO instruction in that if EE is zero polling will continue despite any mismatch.

There is also a mode in which the programmer can force the polling to stop at the end of the current cycle. This involves setting the UPDATE and ERROR ENABLE bits in the control register. When the polling cycle is complete, polling will stop and an interrupt will be generated.

The DOC instruction is used to set and clear the bits in the control register. This instruction can be executed at any time, independently of whether polling is in progress.

The DIC instruction is used to read various status lines in the interface, and is useful primarily for diagnostic purposes. The format and definition of these bits is given in the Appendix.

Whenever polling stops and an interrupt is generated, BUSY is zero and DONE is 1 as in the standard Data General I/O protocol. When the interface is in this condition, the 8 words of status information can be read by means of successive DIAs. It is incorrect to try to read words while polling is in progress (i.e., if BUSY is set). The first DIA retrieves word 1, the second word 2, etc. The programmer can read as many of the 8 words as are desired. There is no requirement to read them all or to read any. If reading continues beyond word 8, word 1 will be obtained on all subsequent DIAs.

Setting BUSY restarts the polling cycle, and resets the status formatter buffer address register so that the next DIA will retrieve word 1.

Note that because the status formatter compares successive status bytes to determine whether or not it should interrupt, interrupts may be generated when the status formatter is first activated or when one of the devices it monitors is first turned on. Normally this is not desired, and the following sequence of commands will prevent interrupts until the status has stabilized.

DOCS EE = 0, UPDATE = 0

Wait until the status has had time to stabilize

DOC EE = 1. UPDATE = 0

Please see the Appendix for the format and definition of the status information.

The status formatter also has a self-diagnostic mode. By setting the Inhibit Polling bit (IP) in the control register by means of a DOC instruction, the status formatter is prevented from polling the devices. Instead it loads into the status words either all ones or all zeros. The choice is determined by the value of the Test Data (TD) bit, 0 giving zeros, and 1 giving ones. The status formatter memory and much of the data transmission circuits can be checked by reading this data back and checking that it matches the expected value.

#### 8.0 UNIVERSAL INTERVAL TIMER

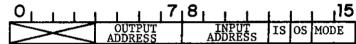

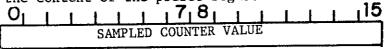

The Universal Interval Timer (UIT) provides a means to interrupt the computer at software controlled intervals. The UIT provides timing accurate to 1 µsec. Its timing is derived from the ARIES 16 MHz clock. The UIT counter counts from zero or a software specified preset value up to 65535. On the next count it wraps around to zero and an interrupt is generated by the carry out of the high order bit. Even though an interrupt is generated, the counter may continue running, depending on the contents of the control register.

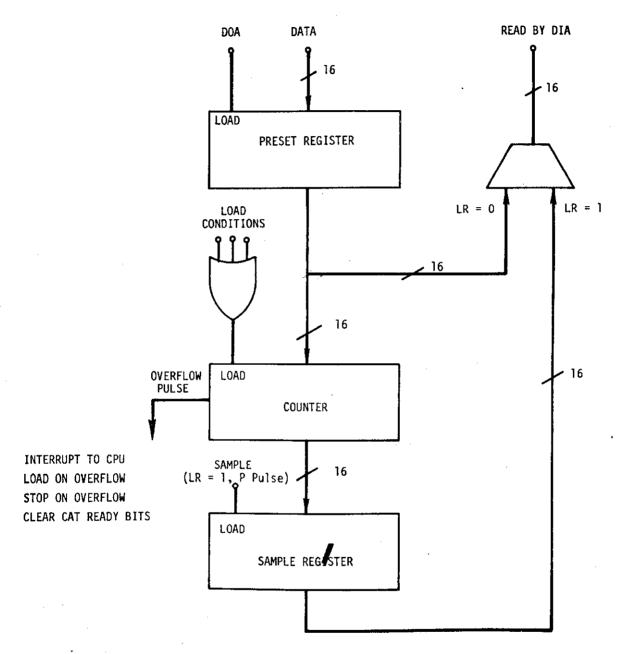

Figure 8.1 shows the major UIT registers (with the exception of the control register) and their relationships. This is not a complete diagram of the UIT, and it intends to show the general data flow and not the exact electrical connections.

To provide an initial 16 bit count value for the UIT (called its preset value) a DOA instruction is used. This value is saved by the UIT in the preset register, allowing the counter to be repeatedly started at this value without requiring further DOAs.

The DOC instruction is used to set or reset the bits in the UIT control register. The current state of this register can be read by means of a DIC instruction. The bits in this register have the following functions when set (except where separate functions are shown for 0 and 1):

- 0-8: Unused

- 9: Load the counter on an external signal.

- 10: Load the counter on overflow.

- 11: Stop the counter on overflow.

- 12: Load (0) or read (1) the counter.

P line must also be pulsed for these to

- 14: Zero the counter. pulsed for these to

- 15: Start (0) or stop (1) the counter. take effect.

All of these bits can be set or reset at any time, whether or not the counter is running. Bits 12-14 take effect whenever the P line is pulsed, whether or not the counter is running. To load the counter means to take the last preset value stored by a DOA instruction and load it into the counter. Overflow occurs when the counter wraps around from 65535 to zero, causing an interrupt. The external signal is an external electrical connection of the UIT. Pulses on that line can be used to trigger a load operation if bit 9 is set. In ARIES, this line is connected to the receiver and is pulsed whenever an ATCRBS/All-Call interrogation is received.

Bits 12 and 13 operate together to load the counter. By setting bit 12 to zero and bit 13 to 1, and pulsing the P line, the counter can be loaded with the preset value.

Fig.8.1. Major UIT Registers.

The current counter value can be read by setting bit 12 to 1, and pulsing the P line. This causes the current counter value to be sampled and saved in the sample register of the UIT. This action takes place regardless of the state of bit 13. This value can then be read by means of a DIA instruction. Bit 12 of the control register must remain set while this DIA is executed, or no valid data will be read. Whenever a DIA is executed with bit 12 set, the last counter value sampled will always be read. Reading the counter in this way does not stop it.

To generate an interrupt after a specific interval of T  $\mu$ sec, the programmer must preset the counter to 65536-T and start it running (if it is not already doing so). Since the Eclipse is a 16 bit machine using 2's complement arithmetic, this is equivalent to loading (- T). The BUSY bit must also be set in order to receive the interrupt, as the standard Data General BUSY/DONE logic is used for generating the interrupt. The BUSY bit has no effect on the operation of the counter itself.

To generate periodic interrupts at intervals of T  $\mu$ sec, the above procedure must be followed and in addition bit 10 of the control register must be set. Note that BUSY must be set again after each interrupt, or interrupts after the first one will be lost.

#### 9.0 RANDOM NUMBER GENERATOR

The purpose of this device is to provide rapid generation of random numbers. It is extremely easy to use, successive DIA instructions returning successive 16 bit uniformly distributed random integers. The BUSY/DONE logic is not used, and no interrupts are generated.

Since the number generator is only pseudo-random, it can be made to repeat the same sequence of numbers by reinitializing it. This is accomplished by the I/O RESET pulse or by pulsing the P line.

### References

- 1. M. Goon and D.A. Spencer, "The Aircraft Reply and Interference Environment Simulator (ARIES) Vol. 1: Principles of Operation", Project Report ATC-87, Volume 1, Lincoln Laboratory, M.I.T. (22 March 1979), FAA-RD-78-96.

- 2. D. Reiner and H.F. Vandevenne, "Provisional Message Formats for the DABS/NAS Interface (Revision 1)", Project Report ATC-33, Revision 1, Lincoln Laboratory, M.I.T. (10 October 1974), DDC AD-A000257/6.

- 3. Programmer's Reference Manual, Eclipse Line Computers, Data General Corporation, 015-000024.

- Programmer's Reference Manual, Peripherals, Data General Corporation, 015-000021.

- 5. Technical Reference, Programmable Synchronous Line Adapters, Data General Corporation, 014-000015.

- 6. Interface Designer's Reference, Nova and Eclipse Line Computers, Data General Corporation, 015-000031.

#### APPENDIX: DEVICE SUMMARIES AND DATA FORMATS

The following pages summarize the function of all the Lincoln Laboratory constructed I/O devices in the ARIES system. For a more complete description of device operation, please see the appropriate section in the main part of the manual, and also Ref. 1.

In the summaries, the functions START, CLEAR, P, and I/O RESET are represented by S, C, P, and IORST respectively. In describing the effect of pulsing these lines, those functions that are standard among all devices connected to the Eclipse I/O system have been omitted. These functions are as follows:

- S: Sets BUSY, clears DONE, and clears any pending interrupt from the addressed device.

- C: Clears BUSY, DONE, and any pending interrupt from the addressed device.

- P: This line has no standard function.

- IORST: Performs all the functions of CLEAR, and in addition clears the interrupt mask. This line affects all devices, and cannot be addressed to a particular device.

In the data format descriptions the following symbol is used to represent undefined, "don't care", fields:

Also, in several of the discussions, the term "set" is used in reference to flip-flops or bits to mean "set to 1", and "reset" to mean "set to 0".

In the descriptions of certain fields, additional information is included describing how the ARIES real time software uses these fields.

## SUMMARY OF DEVICE NUMBER AND MASK BIT ASSIGNMENTS

| Device Code (octal) | Mask Bit                                  |

|---------------------|-------------------------------------------|

| 10                  | 14                                        |

| 11                  | 15                                        |

| 33                  | 7                                         |

| 22                  | 10                                        |

| 30                  | 14                                        |

| 17                  | 12                                        |

| 14                  | 13                                        |

|                     |                                           |

| 46                  | *                                         |

| 50                  | 2                                         |

| 52                  | 3                                         |

| 54                  | 4                                         |

| 56                  | 5                                         |

| 60                  | * .                                       |

| 44                  | 11                                        |

| 62                  | 9                                         |

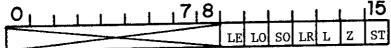

|                     | 10 11 33 22 30 17 14 46 50 52 54 56 60 44 |

<sup>\*</sup>These devices do not generate interrupts.

As is standard for all Data General and ARIES documentation, bit  $\theta$  is the high order bit, and bit 15 is the low order bit.

Device: Receiver

Device Number (octal): 52

Mask Bit: 3

- S: Clears the second DONE flip-flop, and activates the receiver.

- C: Clears the second DONE flip-flop, deactivates the receiver, and clears the interrogation counter.

- P: Clears the second DONE flip-flop, thereby clearing the interrogation interrupt.

- IORST: The second DONE flip-flop is cleared and the interrogation counter is cleared. This signal has no effect on the buffer address pointer, or on the memory address register. These must be explicitly initialized by a DOA instruction.

Note: The interrogation counter is zeroed whenever BUSY=0.

The second DONE flip-flop is set whenever an interrogation is received, causing an interrupt. The primary DONE flip-flop is set to indicate buffer overflow. The interrupts caused by these can be distinguished by using the I/O SKIP instruction to test the primary DONE flip-flop. (I/O skip will not skip if only the second DONE flip-flop is set).

DOC: Decrements the interrogation counter. No data is transferred, and so the content of the register specified as the argument of the DOC does not matter.

#### RECEIVER

| Field                                 | Significance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATCRBS/ALL-CALL<br>INTERROGATION TIME | The time since the last ATCRBS/DABS All-Call interrogation; LSB = 1 µsec. Only used to measure the interrogation interval and therefore does not need range-clock resolution.                                                                                                                                                                                                                                                                                                                                                                                                    |

| DISCRETE<br>INTERROGATION<br>TIME     | The time since the last ATCRBS/DABS All-Call interrogation modulo 4.096 msec; LSB = $1/16~\mu sec$ . Used to calculate discrete reply times; therefore, range-clock resolution is required.                                                                                                                                                                                                                                                                                                                                                                                      |

| FB .                                  | Front/back bit. Indicates which antenna, front or back, transmitted the interrogation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                       | 0 Front Antenna<br>1 Back Antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ITYPE                                 | Interrogation type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| gation. A                             | Decimal  Value  Significance  0  Used to indicate an illegal uplink type.  1  ATCRBS/DABS All-Call, Mode A.  2  ATCRBS/DABS All-Call, Mode C.  3  DABS-only All-Call.  4  DABS surveillance (56 bits).  5  ATCRBS Mode A (no P <sub>4</sub> pulse).  6  ATCRBS Mode C (no P <sup>4</sup> pulse).  7  ATCRBS Mode D (no P <sub>4</sub> pulse).  8  DABS COMM-A (112 bits).  9-15  Undefined.  LSB = 2π/2 <sup>14</sup> radian; measured clockwise from true north.  following fields are included in a DABS discrete interrodetailed description of these fields and their use by |

| DL AKIES appea                        | rs in Ref. 1.  DABS lockout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                       | 00 Clear all DABS lockouts. 01 Lockout Mode A and Mode C All-Calls. 10 Lockout auxilliary interrogations (ignored by ARIES). 11 Lockout auxilliary interrogations and standard All-Calls (treated like 01 by ARIES).                                                                                                                                                                                                                                                                                                                                                             |

|   | Field        | Significance                                                                                                                                                           |

|---|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | AL           | ATCRBS lockout. Ignored by ARIES.                                                                                                                                      |

|   | S            | Synchronization indicator (synchro-DABS).                                                                                                                              |

|   |              | <ul> <li>Unsynchronized interrogation. AI, RL, MSRC appear in the following bits.</li> <li>Synchronized interrogation. EPOCH appears in the following bits.</li> </ul> |

|   | AI           | Altitude/identity bit.                                                                                                                                                 |

|   | •            | 0 Reply with Mode C altitude. 1 Reply with Mode A code.                                                                                                                |

|   | RL           | Reply length requested.                                                                                                                                                |

|   |              | O Surveillance reply (56 bits). COMM-B reply (112 bits).                                                                                                               |

|   | MSRC         | Air-to-ground data link message source. Ignored by ARIES.                                                                                                              |

| : | ЕРОСН        | Synchro-DABS epoch. Merely copied into corresponding reply field.                                                                                                      |

|   | СР           | Clear PBUT. If set to 1, clears the transponder's pilot acknowledgment.                                                                                                |

|   | СВ           | Clear B bit. If set to 1, clears the transponder's downlink request.                                                                                                   |

|   | SP .         | Spare bit, ignored by ARIES.                                                                                                                                           |

|   | SD (ALEC)    | Special data, or altitude echo field. Ignored by ARIES.                                                                                                                |

|   | MA           | COMM-A message field. Ignored by ARIES except for the bit marked AR, which initiates the acknowledgment request protocol if set to 1.                                  |

|   | DABS ADDRESS | A 24-bit transponder identifier. The low order 10 bits are used by ARIES as a track number.                                                                            |

Device: Controlled Reply Generator

Device Number (octal): 46

Mask Bit: None (this device does not generate interrupts).

S.C: Not used. The BUSY/DONE logic is not used by this interface.

P: Used in conjunction with the DOA or DOB instruction which transfers the last word of a reply (word 4 for ATCRBS, 10 for DABS). This increments the reply counter for the current primary or secondary memory, depending on whether it is associated with DOA or DOB respectively. The result is undefined if P is used other than with a DOA or DOB instruction.