# Project Report ATC-115

# **General Aviation TCAS Avionics** (GATCAS)

R. L. Briggs J. DiBartolo D. I. Underwood D. J. Callahan

17 February 1984

# **Lincoln Laboratory**

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Lexington, Massachusetts

Prepared for the Federal Aviation Administration, Washington, D.C. 20591

This document is available to the public through the National Technical Information Service, Springfield, VA 22161 This document is disseminated under the sponsorship of the Department of Transportation in the interest of information exchange. The United States Government assumes no liability for its contents or use thereof.

| 1. Report No.                                                                           | 2.                                       | Government Accession No.                                                     | 3. Re                                                                                                                                                                 | cipient's Catalog No.                     |                            |

|-----------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------|

| •                                                                                       |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

| DOT/FAA/RD-82/86                                                                        | 1.                                       |                                                                              |                                                                                                                                                                       |                                           |                            |

| 4. Title and Subtitle                                                                   |                                          |                                                                              |                                                                                                                                                                       | port Date                                 |                            |

| 4. Title and Subtine                                                                    |                                          |                                                                              | 11                                                                                                                                                                    | 7 February 1984                           |                            |

| General Aviation TCAS Avionics (GATCAS)                                                 |                                          |                                                                              | 6. Pa                                                                                                                                                                 | rforming Organization Code                |                            |

|                                                                                         |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

| 7. Author(s)                                                                            |                                          | ·                                                                            | 8. Pc                                                                                                                                                                 | rforming Organization Repor               | t No.                      |

|                                                                                         | ald I. U                                 | Inderwood                                                                    | ١.                                                                                                                                                                    | TC 115-                                   |                            |

| Joseph DiBartolo Den                                                                    | nis J. C                                 | allahan                                                                      | A                                                                                                                                                                     | TC-115                                    |                            |

| 9. Performing Organization Name and Address                                             |                                          |                                                                              | 109                                                                                                                                                                   | Vork Unit No                              |                            |

| -                                                                                       |                                          |                                                                              | H H H                                                                                                                                                                 |                                           |                            |

| Lincoln Laboratory, M.I.T.                                                              |                                          |                                                                              | 11. C                                                                                                                                                                 | entract or Grant No.                      |                            |

| P.O. Box 73<br>Lexington, MA 92173-9073                                                 |                                          |                                                                              | <b>D</b>                                                                                                                                                              | OT-FA72WAI-877                            |                            |

| Lexington, MA 302110-0010                                                               |                                          |                                                                              | 13. 1                                                                                                                                                                 | ype of Report and Period Co               | vered                      |

| 12. Sponsoring Agency Name and Address                                                  |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

| Department of Transportation                                                            |                                          |                                                                              | · P                                                                                                                                                                   | roject Report                             |                            |

| Federal Aviation Administration                                                         |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

| Systems Research and Developme                                                          |                                          | vice                                                                         | 14. S                                                                                                                                                                 | ponsoring Agency Code                     |                            |

| Washington, DC 20591                                                                    |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

| FAA at M.I.T. Lincoln I equipment was develope aviation usage.  The experimental ge     | aborato<br>ed was t<br>neral av<br>ammed | ory are described.  o assess the feasib  iation TCAS (GA' sequencer, a 16-bi | dance System (TCAS) avid<br>The objective of the prog<br>ility of providing a small,<br>ICAS) avionics incorporat<br>t microprocessor and a lo<br>d to employ GATCAS. | ram under which low-cost unit for g       | this<br>general<br>chitec- |

| craft/nmi <sup>2</sup> , and to provi<br>time of 10 seconds and a<br>GATCAS is 3.4 nmi. | de a pil<br>maxim                        | ot warning time (<br>um closing speed                                        | te below 10,000 feet in der $ m TAU_R)$ of 25 seconds. Assuof 300 knots, the required alysis for general aviation                                                     | iming a track acqu<br>I theoretical range | usition                    |

| 17. Key Words ATC avionics                                                              |                                          |                                                                              | 18. Distribution Statement                                                                                                                                            |                                           |                            |

| FAA beacon equipment Document is available to the public through                        |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

| Threat alert                                                                            |                                          |                                                                              | the National Technica                                                                                                                                                 | ıl Information Ser                        | vice,                      |

| Collision avoidance                                                                     |                                          |                                                                              | Springfield, Virgina 2                                                                                                                                                | 2161.                                     |                            |

| Equipment cost                                                                          |                                          |                                                                              |                                                                                                                                                                       |                                           |                            |

|                                                                                         | ······································   | 20 Canada Olivert (2.42.44)                                                  | le pezel                                                                                                                                                              | 21. No. of Pages                          | 22. Price                  |

| 19. Security Classif. (of this report)                                                  | • ]                                      | 20. Security Classif. (of th                                                 | iz hađa)                                                                                                                                                              |                                           |                            |

| Unclassified                                                                            | 1                                        | Unclassified                                                                 |                                                                                                                                                                       | 104                                       |                            |

# Unclassified

#### ERRATA SHEET

#### PROJECT REPORT ATC-117

Please make the following page changes to Project Report ATC-117 entitled: "Fundamentals of Mode S Parity Coding".

Pages 34 and 35 should be removed and replaced with the attached pages 34 and 35.

28 May 1986

Publications Office M.I.T. Lincoln Laboratory P.O. Box 73 Lexington, MA 02173-0073

# Unclassified

# CONTENTS

|     |      |                                                                | Page     |

|-----|------|----------------------------------------------------------------|----------|

| 1.0 | INTR | CODUCTION                                                      | 1        |

| 2.0 | GATO | CAS DESIGN                                                     | 2        |

| 4.0 |      | Overview                                                       | 2        |

|     |      | 2.1.1 Design Philosophy                                        | 2        |

|     |      | 2.1.2 System Operating Characteristics                         | 3        |

|     |      | 2.1.3 Major System Elements                                    | 3        |

|     | 2.2  | RF Unit                                                        | 7        |

|     |      | 2.2.1 Microwave Signal Source (1030 MHz)                       | 7        |

|     |      | 2.2.2 PAM/DPSK Modulators                                      | 9        |

|     |      | 2.2.3 Microwave Power Module                                   | 9        |

|     |      | 2.2.4 Other Transmitter RF Components                          | 9        |

|     |      | 2.2.5 Receiver                                                 | 11       |

|     | 2.3  | Video-Pulse Quantizer                                          | 11       |

|     | 2.4  | Reply Detector                                                 | 14       |

|     |      | 2.4.1 General Description                                      | 14       |

|     |      | 2.4.2 Digitizer Clock Control                                  | 18       |

|     |      | 2.4.3 Video Digitizer                                          | 18<br>18 |

|     |      | 2.4.4 Sliding Window Detector                                  | 25       |

|     |      | 2.4.5 Mode S Preamble Detector                                 | 23       |

|     |      | 2.4.6 Pseudo Leading Edge Generation and Short                 | 25       |

|     |      | Pulse Rejection                                                | 31       |

|     | 2.5  | Reply and Interrogation Controller                             | 31       |

|     |      | 2.5.1 General Description 2.5.2 Am 2910 Microprogram Sequencer | 31       |

|     |      | 2.5.3 Am 2914 Interrupt Controller                             | 34       |

|     |      | 2.5.4 Microprogram Memory                                      | 35       |

|     |      | 2.5.5 Control Register                                         | 35       |

|     |      | 2.5.6 Status Register                                          | 38       |

|     |      | 2.5.7 Range Counter Latch                                      | 38       |

|     |      | 2.5.8 Mode S Data Memory                                       | 38       |

|     | 2.6  | Mode S Interrogation Generator (DIG)                           | 41       |

|     | 2.0  | 2.6.1 General Description                                      | 41       |

|     |      | 2.6.2 Mode S DPSK Encoder                                      | 41       |

|     | 2.7  | ( \)                                                           | 41       |

|     |      | 2.7.1 General Description                                      | 41       |

|     |      | 2.7.2 Mode S Downlink Decoder                                  | 43       |

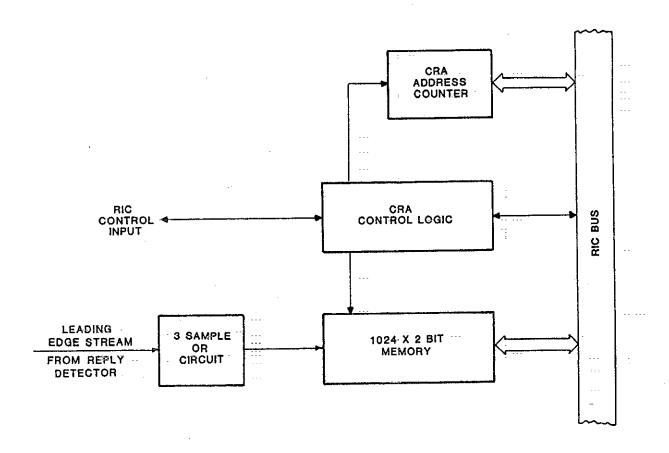

|     | 2.8  | Mode C Reply Accumulator                                       | 43       |

|     |      | 2.8.1 General Description                                      | 43       |

|     |      | 2.8.2 CRA Storage Memory                                       | 43       |

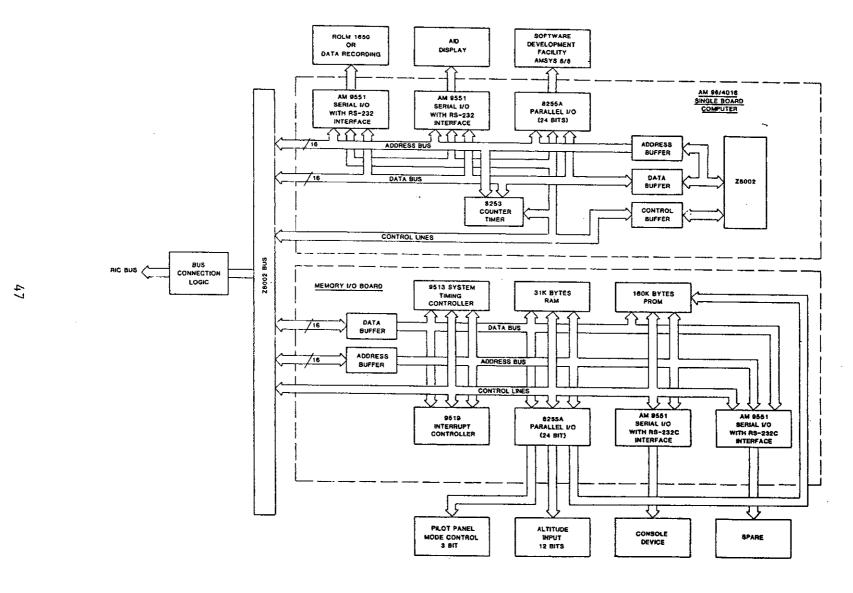

|     | 2.9  | Computer Subsystem                                             | 46       |

|     |      | 2.9.1 General Description                                      | 46<br>46 |

|     |      | 2.9.2 Z8002 Microprocessor                                     | 48       |

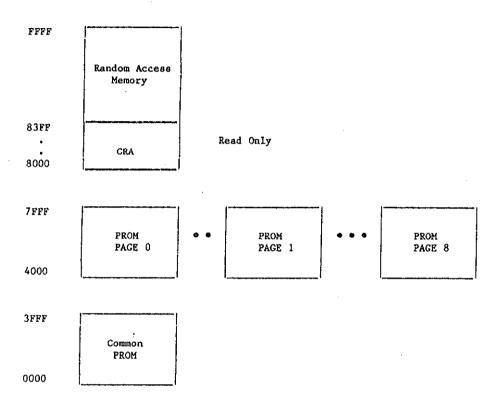

|     |      | 2.9.3 System Memory                                            | 48       |

|     |      | 2.9.4 I/O Address Space                                        | 48       |

|     |      | 2.9.5 Am8255A Parallel I/O Port                                | 40       |

# CONTENTS (Cont'd)

|     |      |                                        | Page     |  |  |

|-----|------|----------------------------------------|----------|--|--|

|     |      | 2.9.6 Am9551 Serial I/O Port           | 52       |  |  |

|     |      | 2.9.7 Am9519A Interrupt Controller     | 52       |  |  |

|     |      | 2.9.8 Am9513 System Timing Controller  | 52       |  |  |

|     |      | 2.9.9 Am8253 Counter Timer             | 52       |  |  |

|     |      | 2.9.10 Bus Connection Logic            | 53       |  |  |

| 3.0 | GATC | CAS SOFTWARE                           | 54       |  |  |

| ••• |      | Overview                               | 54       |  |  |

|     |      | Real-Time Microprocessor Software      | 54       |  |  |

|     |      | 3.2.1 Task Scheduler and I/O Handler   | 54       |  |  |

|     |      | 3.2.2 Task Directives                  | 55       |  |  |

|     |      | 3.2.2.1 Create Task (RTSK)             | 55       |  |  |

|     |      | 3.2.2.2 Mark Wait (MARKWT)             | 55       |  |  |

|     |      | 3.2.2.3 Mark Return (MARKRT)           | 55       |  |  |

|     |      | 3.2.2.4 Update Time (UPDTM)            | 55       |  |  |

|     |      | 3.2.2.5 Wait for Flag (WAITF)          | 56       |  |  |

|     |      | 3.2.2.6 Change Priority (CBGPRI)       | 56       |  |  |

|     |      | 3.2.2.7 Transmit (XMITR)               | 56       |  |  |

|     |      | 3.2.2.8 Receiver (RCVR)                | 56       |  |  |

|     |      | 3.2.2.9 Flush Buffer (FLUSH)           | 57       |  |  |

|     |      | 3.2.2.10 Simulate Input (SIMIN)        | 57<br>57 |  |  |

|     |      | 3.2.3 Mode C Processing                | 60       |  |  |

|     |      | 3.2.4 Mode S Processing                | 60       |  |  |

|     |      | 3.2.5 Squitter Processing              | 60       |  |  |

|     |      | 3.2.6 TEU Data Communications          | 60       |  |  |

|     |      | 3.2.6.1 Interface Protocol and Formats | 61       |  |  |

|     |      | 3.2.6.2 TEU Input and Output Handlers  | 61       |  |  |

|     |      | 3.2.6.3 GATCAS Input and Output Tasks  | 64       |  |  |

|     | 3.3  | Real-Time Microprogram Software        | 64       |  |  |

|     |      | 3.3.1 General Description              | 64       |  |  |

|     |      | 3.3.2 Mode C Processing                | 64       |  |  |

|     |      | 3.3.3 Mode S Processing                | 70       |  |  |

|     |      | 3.3.4 Squitter Processing              |          |  |  |

| 4.0 | DIAG | NOSTIC HARDWARE                        | 72       |  |  |

| 5.0 | DIAG | DIAGNOSTIC SOFTWARE                    |          |  |  |

|     | 5.1  | General Description                    | 74       |  |  |

|     | 5.2  | Z8002 System Diagnostics               | 74       |  |  |

|     | 5.3  |                                        | 75       |  |  |

|     |      | 5.3.1 Mode C Diagnostics               | 76       |  |  |

|     |      | 5.3.2 Mode S Diagnostics               | 77       |  |  |

|     | 5.4  | TEU Diagnostics                        | 77       |  |  |

# CONTENTS (Cont'd)

|      |       |         |                                               | Page |

|------|-------|---------|-----------------------------------------------|------|

| 6.0  | FLIG  | HT TEST | RESULTS                                       | 79   |

|      | 6.1   | Mode S  | Performance                                   | 79   |

|      | 6.2   | Mode C  | Mode Performance                              | 79   |

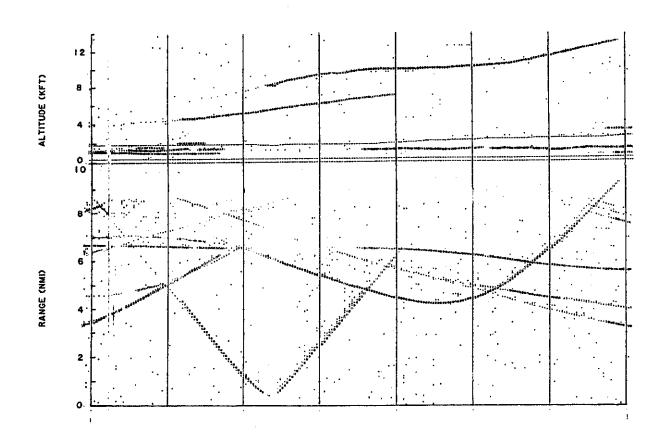

|      | • • • |         | Detection at Long Range                       | 79   |

|      |       | 6.2.2   | Statistical Performance Assessment            | 83   |

|      |       |         | 6.2.2.1 Performance Definitions               | 83   |

|      |       |         | 6.2.2.2 Probability of Report                 | 83   |

|      |       | 6.2.3   | Probability of Track                          | 85   |

|      |       |         | Performance as a Function of Aircraft Density | 85   |

| REFE | RENCE | S       |                                               | 92   |

| APPE | NDIX  | A GA    | ATCAS COST ESTIMATE                           | A-1  |

# ILLUSTRATIONS

| Fig.           |                                                                                                          | Page             |

|----------------|----------------------------------------------------------------------------------------------------------|------------------|

| 2.1-1          | GATCAS collision avoidance unit                                                                          | 4<br>5           |

| 2.1-2<br>2.1-3 | GATCAS operational configuration GATCAS architecture                                                     | 6                |

| 2.1-3          | GATCAS atchitecture                                                                                      | Ū                |

| 2.2-1<br>2.2-2 | General aviation TCAS microwave block diagram Typical DPSK phase transition (180° phase reversal). Input | 8                |

| 210 2          | to 150W amplifier (a), output of 150 watt amplifier (b).                                                 | 10               |

| 2.2-3          | GATCAS receiver log video response                                                                       | 13               |

| 2.3-1          | VPQ block diagram                                                                                        | 15               |

| 2.3-2          | VPQ waveforms                                                                                            | 16               |

| 2.3-3          | ATCRBS DMTL                                                                                              | 17               |

| 2.3-4          | Mode S DMTL                                                                                              | 17               |

| 2.4-1          | Digitizer clock control                                                                                  | 19               |

| 2.4-2          | Digitizer logic                                                                                          | 20               |

| 2.4-3          | Trailing edge conditions                                                                                 | 21               |

| 2.4-4          | Digitizer timing                                                                                         | 22               |

| 2.4-5          | Sliding window detector                                                                                  | 23               |

| 2.4-6          | Mode S preamble detection timing                                                                         | 24               |

| 2.4-7          | Mode S preamble detector                                                                                 | 26<br>27         |

| 2.4-8          | Pseudo and extra leading edge generators                                                                 | 27<br>28         |

| 2.4-9          | Pseudo and extra leading edge generation                                                                 | 20<br>29         |

| 2.4-10         | Pseudo leading edge generation, PW = 6                                                                   | 29               |

| 2.4-11         | Pseudo leading edge generation, PW = 10                                                                  | 30               |

| 2.4-12         | Extra leading edge timing                                                                                | 30               |

| 2.5-1          | Reply and interrogation controller (RIC) block diagram                                                   | 32               |

| 2.5-2          | Block Diagram of Am2910                                                                                  | 33               |

| 2.5-3          | Microprogram field definitions of the signal processor                                                   | 36               |

| 2.5-4          | RIC control register field description                                                                   | 37<br>37         |

| 2.5-5          | RIC task control field assignments                                                                       | 3 <i>7</i><br>39 |

| 2.5-6          | Status bit definitions                                                                                   | 40               |

| 2.5-7          | Special I/O address assignments                                                                          | 40               |

| 2.6-1          | Mode S interrogation generator feed-out encoder                                                          | 42               |

| 2.7-1          | Mode S reply processor feed-out decoder                                                                  | 44               |

| 2.8-1          | Mode C reply accumulator (CRA)                                                                           | 45               |

| 2.9-1          | Computer subsysystem                                                                                     | 47               |

| 2.9-2          | Z8002 program memory address assignment                                                                  | 49               |

| 2.9-3          | I/O address space assignment                                                                             | 50               |

# ILLUSTRATIONS (CONT'd)

| Fig.   |                                                    | Page |

|--------|----------------------------------------------------|------|

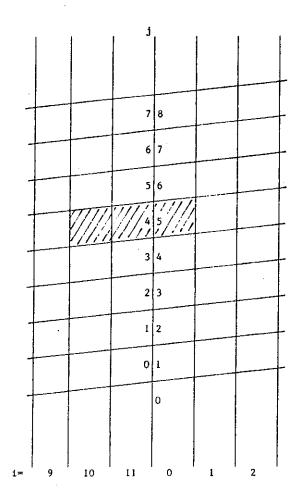

| 3.2-1  | Helical representation of ATCRBS leading edge (LE) |      |

|        | pulse stream                                       | 59   |

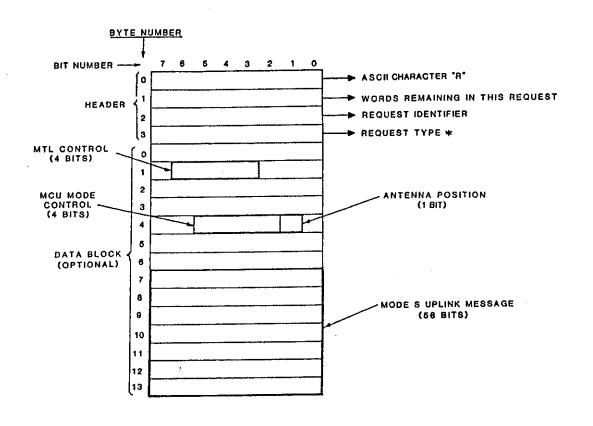

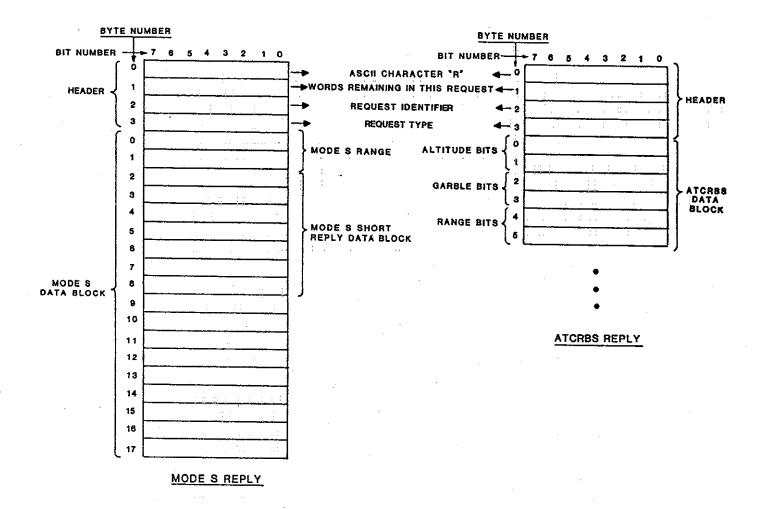

| 3.2-2  | Byte definitions for request formats               | 62   |

| 3.2-3  | Byte definitions for reply formats                 | 63   |

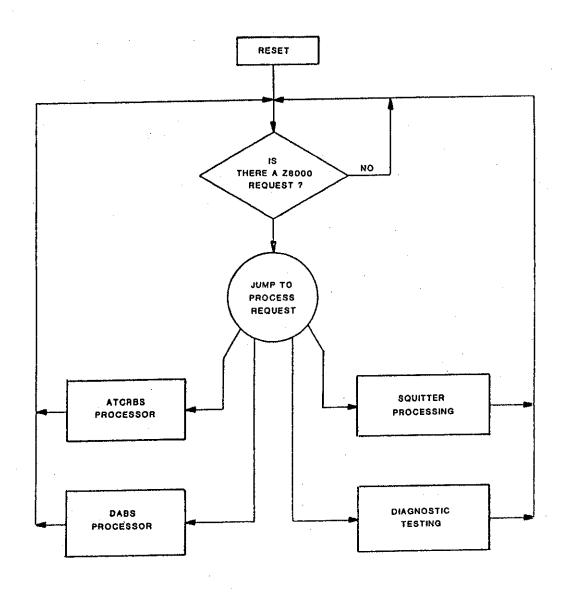

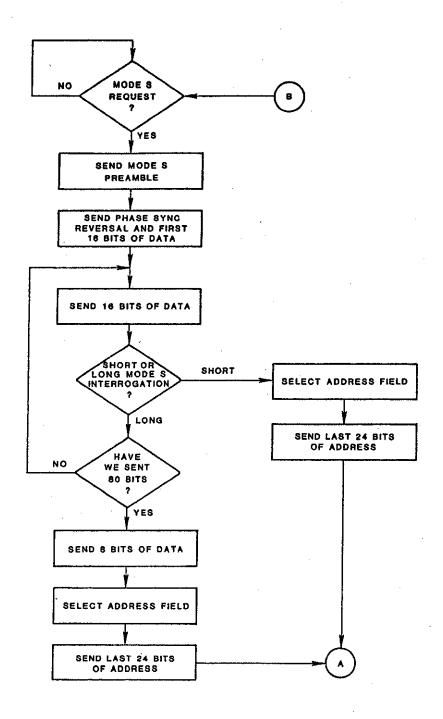

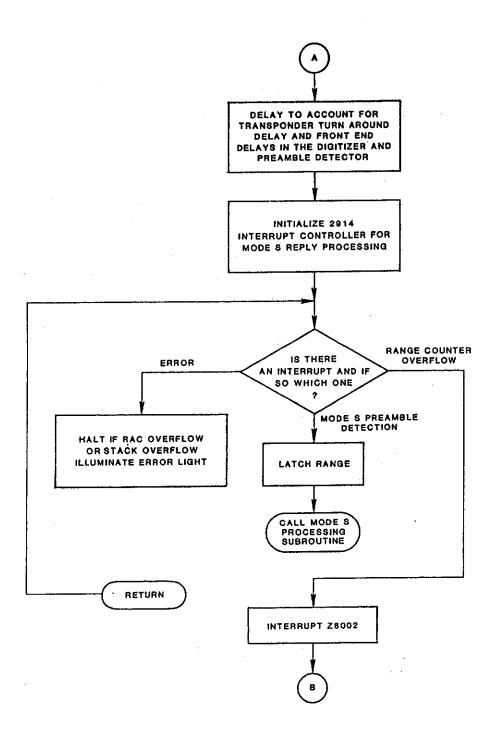

| 3.3-1  | Program flow of the Am2910 microprogram software   | 65   |

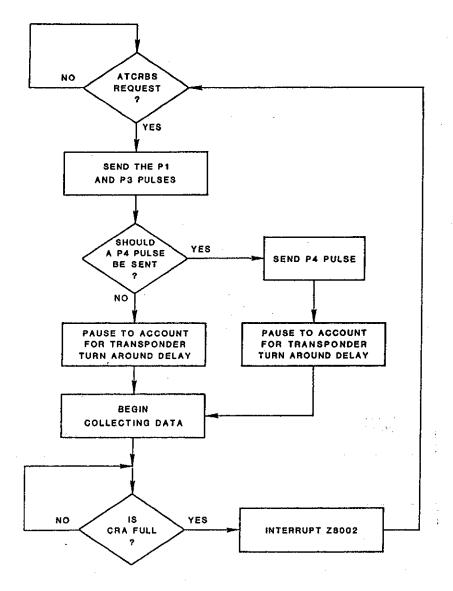

| 3.3-2  | Mode C processing routine                          | 66   |

| 3.3-3a | Mode S processing routine                          | 67   |

| 3.3-3b | Mode S processing routine                          | 68   |

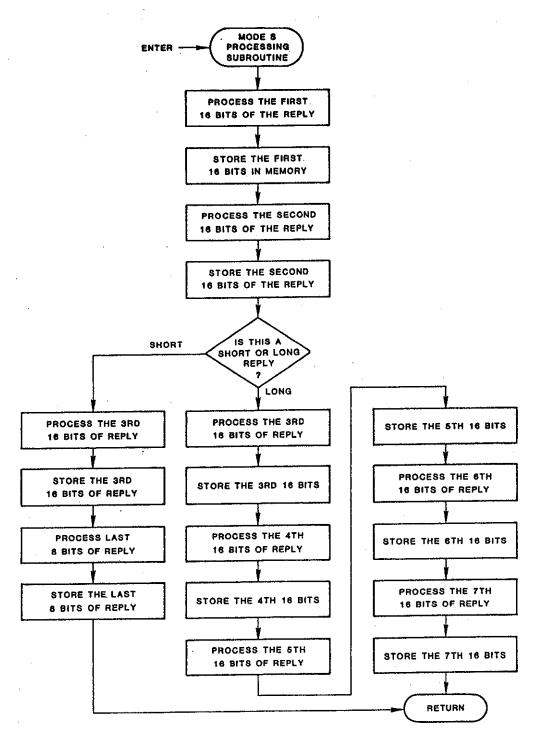

| 3.3-4  | Mode S reply processing subroutine                 | 69   |

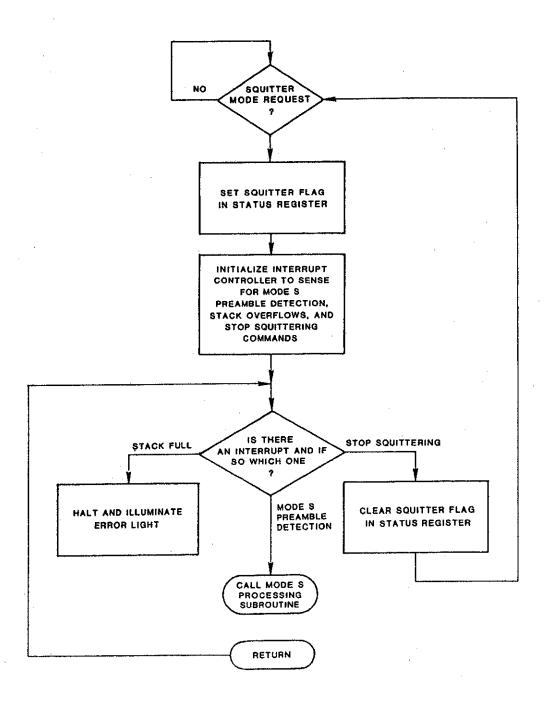

| 3.3-5  | Squitter mode processing routine                   | 71   |

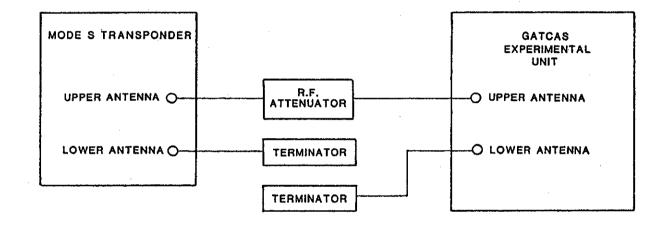

| 4.0-1  | Laboratory test configuration for GATCAS unit      | 73   |

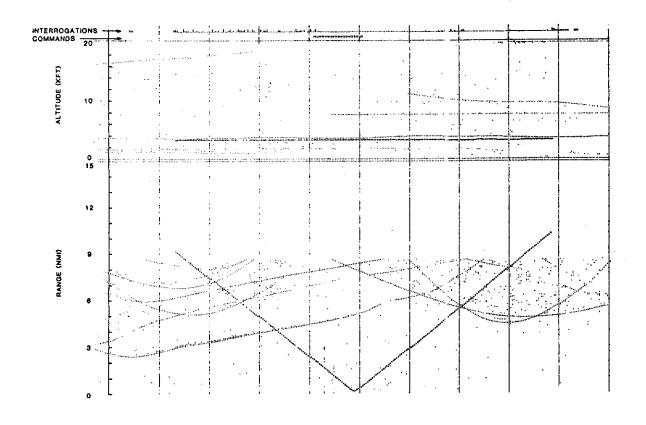

| 6.1-1  | Reply data from Mode S head-on encounter           | 80   |

| 6.1-2  | CAS tracks from Mode S head-on encounter           | 81   |

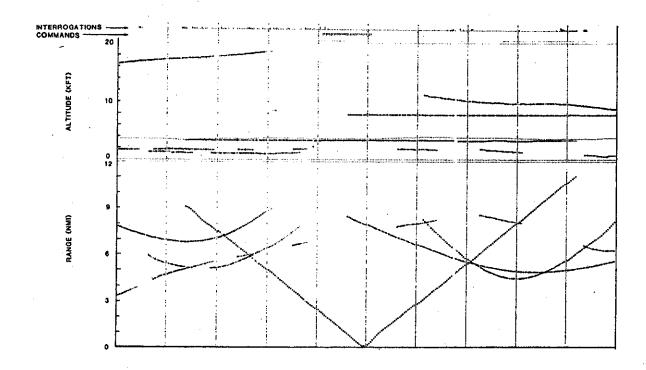

| 6.2.1  | CAS tracks from Mode S head-on encounter           | 82   |

| 6.2-2  | Histogram of the number of targets in track        | 88   |

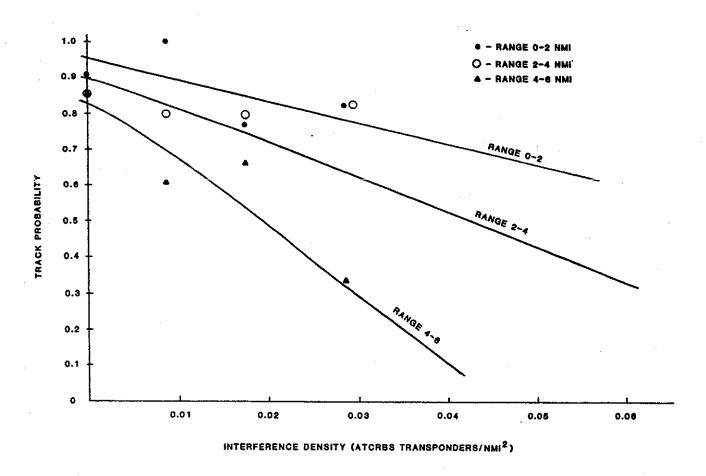

| 6.2-3  | Track probability vs interference density          | 91   |

# TABLES

| Table |                                                                            | Page |

|-------|----------------------------------------------------------------------------|------|

| 2.2-1 | GATCAS RF link power budget                                                | 12   |

| 6-1   | ATCRBS mode performance                                                    | 84   |

| 6-2   | Probability of report evalauted for aircraft of interest                   | 86   |

| 6-3   | Probability of track evaluated for aircraft of interest                    | 87   |

| 6-4   | Probability of track vs. target density evaluated for aircraft of interest | 90   |

| A 1   | GATCAS cost summary                                                        | A-2  |

#### 1.0 INTRODUCTION

Lincoln Laboratory has supported the FAA in the development of Traffic Alert and Collision Avoidance System (TCAS) surveillance techniques for air-carrier use since 1975. In anticipation of an eventual interest in TCAS by the general aviation community, Lincoln Laboratory was tasked in 1979, as a part of its FAA-sponsored TCAS development program, to also explore TCAS surveillance techniques suitable in performance and cost for general aviation use. This report documents the results of this task; it describes the GATCAS equipment that was designed, built, and tested for this program and it provides surveillance performance data from bench tests and flight tests of this equipment.

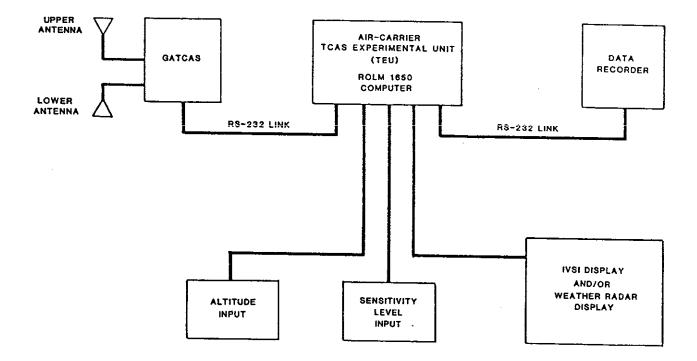

Flight testing of the GATCAS equipment took place during the winter of 1981/1982, and the work was concluded in the Spring of 1982. During the period in which the design specifications for this experimental GATCAS equipment were being developed, significant design concepts were still emerging, many of which were ultimately embodied in the National Standard for TCAS II. The GATCAS equipment that was flown included very few of these concepts and therefore must be considered strictly as an experimental design which was developed to better understand techniques for reducing the cost of critical surveillance elements associated with the TCAS transmitter and the reply processor. The equipment did not include ATCRBS or Mode S surveillance tracking algorithms. It included no interference limiting, bearing estimation, or CAS logic. It was flight tested by interfacing it with an existing air-carrier TCAS Experimental Unit (TEU) which did include ATCRBS and Mode S surveillance algorithms, CAS logic and recording capability, but no interference limiting, bearing estimation, or traffic advisory display logic.

Early paragraphs of Section 2. summarize the GATCAS surveillance design philosophy, list the performance requirements established, and describe the major architecture of the GATCAS avionics subsystems. Succeeding paragraphs in Section 2 describe the design of each of the subunits included in the GATCAS avionics. Section 3 describes the software developed to perform the real-time processing tasks. Diagnostic hardware and software are described in Sections 4 and 5 respectively. Flight test results obtained by interfacing to an existing TEU are presented in Section 6., and Appendix A is an analysis of the probable costs of GATCAS equipment based upon the design concepts employed in the experimental model.

The remainder of this chapter reviews the Mode S material that forms the background to signal coding. The following chapters then present and explain the various components of the overall Mode S coding design.

#### 1.1 Coding Problem

One of the primary responsibilities of Mode S is the delivery and reception of various types of traffic control information to and from aircraft. It is necessary that such messages be validated before acceptance. Air Traffic Control voice radio commands are validated in the present system by repeating the command back to the ground. This same technique could be used with digital messages in Mode S as a low cost method of message validation. However, if a message could be validated in a single transaction, message delivery would require fewer transmissions and thus less channel capacity, and would also be less strongly affected by link reliability. Coding techniques offer just such a means of reliably validating a single transmission, and such coding techniques need not involve a great amount of circuit complexity. Thus, coding techniques were studied from the outset of the Mode S program as a promising means of providing a highly reliable and efficient message validation system with little cost impact on the transponder.

In order to eliminate the overhead associated with the redundant parity check bits in coding, a technique for combining parity and address bits was used as developed by the British in their early work on a discrete address system referred to as the ADSEL (Address Selection) beacon system. Instead of having the receiver check two separate message fields to determine if the received message should be accepted, a combined address/parity field allows the operation to be carried out by checking only one field. Whenever the parity check bits resulting from the received message are nonzero, the expected address/parity field is different from the actual received address/parity field, indicating the message should not be accepted. This scheme removes the overhead associated with the use of coding for message validation, which is an important step because of the constraints on message length.

Although the foregoing discussion makes coding appear attractive for message validation, the key problem is that of selecting a code that performs adequately in the channel environment. There are numerous error mechanisms affecting the Mode S uplink and downlink channels. A decision was made early in the coding investigation to concentrate on codes that can overcome errors caused by interference sources. Errors caused by noise only or caused solely by fading of the signal below threshold were not considered. A rationale for this posture is that errors due to noise alone can be dealt with by virtually any choice of code, while the fading mechanisms that arise from turning aircraft, over-the-horizon transmission, etc., have a duration that is longer than the Mode S message and therefore are beyond the control of any coding scheme.

Errors due to interference arise from ATCRBS interrogations, TACAN channels operating near or harmonically related to 1030 or 1090 MHz, continuous-wave (CW) interference, and multipath. Of these, ATCRBS interference is the dominant factor, and the code search was largely driven

#### 2.1.2 System Operating Characteristics

As noted above, the GATCAS avionics was intended to provide air-to-air surveillance for general aviation aircraft normally operating below 10,000 feet. The operating characteristics selected for the GATCAS experimental unit are summarized as follows:

| Peak Transmit Power (at RF port):<br>Receiver Sensitivity (MTL):<br>Maximum processed | <del>-</del> 72 | watts<br>dBm<br>nmi |

|---------------------------------------------------------------------------------------|-----------------|---------------------|

| ATCRBS Mode Track Capacity (aircraft) Processed and Degarbled:                        | 5               |                     |

| Mode S Mode Track Capacity (aircraft) Active: Dormant: Squitter:                      | 5<br>12<br>25   |                     |

These characteristics provided somewhat more capability than is strictly required for the GATCAS function as summarized in para. 2.1.1. However excess capability was included in this experimental test bed to provide additional experimental flexibility. It was possible to degrade the performance to match the ultimate design goals intended for this class of equipment. The analysis of the surveillance flight test data obtained with this equipment (see Section 6) focused on the performance of the equipment at reduced target ranges.

# 2.1.3 Major System Elements

The GATCAS is a self-contained experimental avionics unit which includes a transmitter-receiver, a digital processor, and a 16-bit computer (Fig. 2.1-1). The computer subsystem is adequate to support surveillance and collision avoidance tasks, and to generate output for display to the pilot. However, to reduce the programming required to make the GATCAS unit functional, an existing air carrier TCAS experimental unit (TEU) was configured to accept reply data from a GATCAS unit serial I/O port so it could perform the real-time processing and recording using existing software. The GATCAS unit thus performed only interrogation control and reply processing in its functional tests. The operational system configuration is shown in Fig. 2.1-2.

The internal architecture of the GATCAS is shown in Fig. 2.1-3. The system is divided into two major components, the computer subsystem and the signal processor. The computer subsystem uses a Z8002 microprocessor and

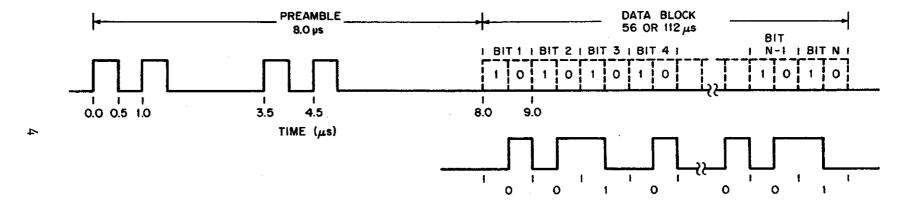

EXAMPLE: REPLY DATA BLOCK WAVEFORM CORRESPONDING TO BIT SEQUENCE 0010...001 SEQUENCE 0010...001

Fig. 1-1. Mode S repyl format.

Fig. 2.1-2. GATCAS operational configuration.

$\mathcal{S}$

Another likely source of interference arises from TACAN interrogation pulse pairs having a carrier frequency close to 1090 MHz (there exist some special use military TACANS using 1090-MHz). These interrogations have two 3.5  $\pm$  0.5 µsec pulses separated by 12.0  $\pm$  0.5 µsec and, again, are seen to result in burst errors spanning less than 24 Mode S bits. Other interference sources such as multipath also lead to bursts of errors in the Mode S message.

The Mode S reply processor uses an amplitude comparator to determine the data from the PPM reply, assigning a '0' or '1' if the first or second chip respectively of the bit has greater amplitude. A separate detector determines whether interference is present for the bit. The data bit is flagged as high confidence if this detector finds (1) that no interference energy is present in the "other" chip, and (2) that the primary chip energy is in the mainbeam of the antenna rather than in a sidelobe. Other bit decisions are labelled as low confidence. The reply azimuth estimate is constructured by averaging the monopulse estimates of the first sixteen high confidence bits.

The confidence measures of the bit decision process are used in the error correction scheme. In particular, by assuming that bit errors can only occur in bits for which a low confidence estimate has been made, the input to the decoder can be characterized as an erasure channel. The correction ability for an erasure channel, in which the possible error locations are known, is the same as the detection ability on a normal channel, in which no such knowledge exists. Thus error correction becomes feasible on the downlink.

provides for two parallel I/O ports, four serial I/O ports, a system timing controller, an interrupt controller and 191 Kbytes of memory. All parts of the computer subsystem are connected using one bus (Z8002 Bus).

The signal processor uses an Am2910 microprogrammed sequencer to control interrogations and replies in both the Mode S and Mode C modes. The signal processor has an internal bus (RIC bus) which connects the Mode S and Mode C memories, range counter, control register, and status register. The Z8002 can read and write to the appropriate registers of the signal processor through the use of bus connection logic which connects the RIC bus to the Z8002 bus.

#### 2.2 RF Unit

The GATCAS RF Unit, Fig. 2.2-1, consists of the following functional subunits:

- a) Microwave signal source

- b) PAM/DPSK modulators

- c) Microwave power module

- d) RF components

- e) Receiver

## 2.2.1 Microwave Signal Source (1030 MHZ)

The microwave signal source consists of a phase-locked, temperature-controlled crystal oscillator, stablized to within ± 0.0005% of the nominal frequency, and a solid state multiplier chain which generates the 1030 MHz transmitter frequency. The output power of the oscillator-multiplier chain is sufficient to permit the insertion of a circulator and a 10-dB pad between the source and the phase-shift modulator (double-balanced mixer). The isolation and the use of an absorptive (rather than reflective) pulse amplitude modulation (PAM) switch are provided to maintain the carrier frequency stability required by the TCAS National Standard.

The microwave source is located in a shielded enclosure to minimize 1030 MHz leakage to the co-located airborne transponder.

The same 1030 MHz frequency source is also used as the receiver local oscillator to convert the 1090 MHz replies to a 60 MHz intermediate frequency (IF).

Parity functions for burst detection codes tend to be quite different from those for random errors. No longer is distance important. Instead, the message bits that generate a specific parity bit must be widely spaced, or said another way, bits within a burst must independently determine different parity bits. A trivial code for detecting burst errors is as follows:

$$p_1 = m_1 + m_{b+1} + m_{2b+1} + \cdots$$

$p_2 = m_2 + m_{b+2} + m_{2b+2} + \cdots$

: (where  $+ =$  sum modulo 2)

$p_b = m_b + m_{2b} + m_{3b} + \cdots$

This parity code detects any burst of up to b-bits, even though its Hamming distance is only 2, implying that it can only guarantee detection of a single random error.

An optimum burst code, such as that chosen for Mode S, will maximize the random error detection performance for a given burst length capability.

#### 2.1 Cyclic Codes

A cyclic code is defined as one in which the set of valid code words is expressible as all multiples of a given generator polynominal G(x):

$$C(x) = H(x) G(x)$$

for any  $H(x)$  (2-1)

where for burst detection applications G(x) will be of the same order as the burst length, namely b. The natural length n of a cyclic code, which is the number of bits each of its code words must contain to produce cyclic code properties, is the smallest integer for which:

$$x^{n}-1$$

----  $\rightarrow$  no remainder

$G(x)$

(2-2)

The code words produced by G(x) will have these n-bits broken up as:

$$n = k + b$$

where k is the number of information bits in the code word and b is the number of parity bits. Each potential code word, produced as in (2-1), is reduced to n-bits by being taken modulo  $x^n-1$ .

Cyclic codes are so-named because any code word, shifted cyclically, is still a code word. That is, if one code word is given by:

$$c_1(x) = H_1(x) G(x) = (a_{n-1} x^{n-1} + a_{n-2} x^{n-2} + \dots + a_1 x + a_0)$$

(2-3)

then a second one can be given by:

#### 2.2.2 PAM/DPSK Modulators

Two types of modulators are required for the RF Unit: a pulse amplitude modulator (PAM), and a differential phase-shift keyed (DPSK) modulator. The PAM modulator consists of an absorptive type switch with an off/on ratio of 110 dB.

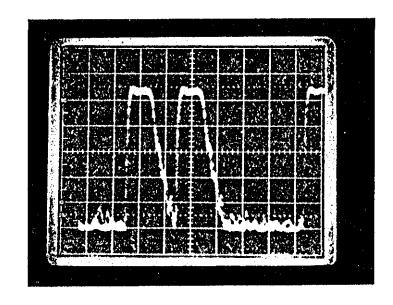

The DPSK modulator consists of a double balanced mixer, and a bipolar video driver. Since the bandwidth of the double-balanced mixer is large relative to the transmit signal bandwidth, the DPSK transition is determined by the rise-time of the driver's video pulse and by the transmitter bandpass characteristics. The Mode S National Standard requires that these transitions be completed within 80 nanoseconds.

#### 2.2.3 Microwave Power Module

The microwave power modules consist of a microwave solid state driver that provides 30 dB of gain at 1030 MHz, and a solid state power amplifier that provides 22 dB of gain. The operating voltage required for the driver is +20 VDC; the operating voltages for the power amplifier are +33 VDC and +50 VDC. These voltages are derived from a common power supply which is energized by the aircraft 28 volt source.

Typical performance of the transmitter is shown in Fig. 2.2-2 which illustrates a transition of the DPSK modulation. It can be seen that the bandwidth of the transmitter is adequate to achieve the required 80 nsec transition time.

#### 2.2.4 Other Transmitter RF Components

The transmitter also includes the following RF transmission and switching devices:

- a) A transmitter output bandpass filter.— This filter, centered at 1030 MHz, has a bandwidth of 20 MHz, an insertion loss of 0.5 dB, provides 60 dB attenuation (with respect to band-center) at the receive frequency (1090 MHz), and limits the transmit spectrum in accordance with the Mode S National Standard.

- b) A circulator. This device acts as diplexer, connecting transmitter, receiver and antennas. It provides at least 25 dB isolation between transmitter and receiver.

- c) A receiver input limiter. This is used for receiver input protection. It can protect against 300 watt peak pulses.

- d) A receiver input bandpass filter (preselector).— This filter is centered at 1090 MHz, has a bandwidth of 20 MHz, and provides 40 dB rejection to unwanted signals at the transmitter frequency (1030 MHz).

Message:

$$1 0 1 1 0$$

lst 5th

bit bit

$= x^4 + x^2 + x$

Generator:  $x^2 + x \rightarrow b = 2$

Encode: find  $x^b M(x) / G(x)$ :

$$x^{4} + x^{3} + 0 + x + 1$$

$$x^{2} + x + 0 \mid x^{6} + 0 + x^{4} + x^{3} + 0 + 0 + 0$$

$$x^{6} + x^{5}$$

$$x^{5} + x^{4} + x^{3}$$

$$x^{5} + x^{4}$$

$$x^{3}$$

$$x^{3} + x^{2}$$

$$x^{2}$$

$$x^{2} + x$$

$$x = R(x)$$

Code Word:

$$x^b M(x) + R(x) = (x^6 + x^4 + x^3) + (x)$$

=  $x^6 + x^4 + x^3 + x$

= 1 0 1 1 0 1 0

| \_\_\_\_\_\_ | | \_\_\_\_\_ |

message parity

Fig. 2-1. Cyclic encoding example.

- e) A diversity switch.— This solid-state SPDT switch connects either the top or bottom mounted antenna, as commanded by surveillance algorithms. It provides 25 dB of inter-channel isolation, and switches in 10 µsec.

- f) Two antenna low pass filters. These low pass filters prevent the radiation of harmonics generated by the diversity switch.

#### 2.2.5 Receiver

The receiver consists of an image filter, a down-converter, a 60 MHz IF filter and a log amplifier.

- a) Down-converter. The insertion loss of the down-converter is 6 dB when +7 dBm LO power is injected to the L-port. The unit can withstand up to +26 dBm at room temperature (+17 dBm at 100°C). The 1 dB compression point occurs when the signal power level at the L-port is 1 mw.

- b) IF amplifier. This is a solid state, modular, wide-band amplifier.

- c) 60 MHz IF filter.- This filter has a bandwidth of 10 MHz and establishes signal and noise bandwidth. It is a 6-pole Bessel filter designed to maintain phase linearity within its 3 dB bandwidth. Its insertion loss is 2 dB.

- d) Log amplifier. The 60 MHz signal is further amplified and video-detected using a miniature log amplifier. Its center frequency is 60 MHz and bandwidth is 20 MHz. Over an input range of -70 to 0 dBm its output rises from 0.2 to 2 volts into 93 ohms, a transfer characteristic of 25.7 mv/dB. The detected output video is fed to the receiver video monitor and the video pulse quantizer (VPQ).

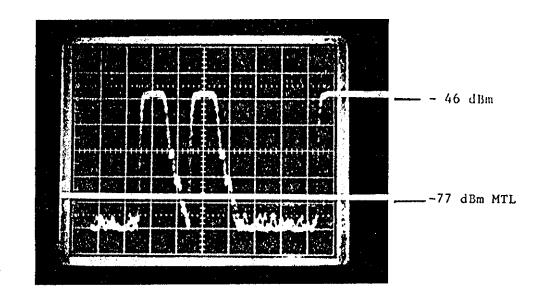

Design of the receiver is based on the power budget and assumptions given in Table 2.2-1. Receiver performance is demonstrated in Fig. 2.2-3a,b,c which indicate a typical receiver log video response for the first two pulses of a Mode S reply preamble at  $-46~\mathrm{dBm}$ .

#### 2.3 Video-Pulse Quantizer

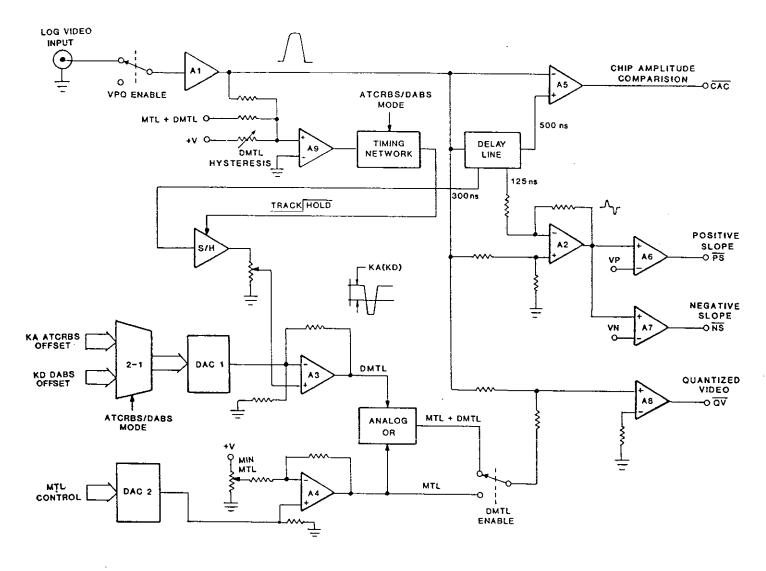

The Video Pulse Quantizer (VPQ) processes receiver log video pulses to produce quantized slope and signal strength, and a Mode S chip amplitude comparison signal. The VPQ is designed to produce, in conjunction with the pulse digitizer described in Section 2.4.3, accurate time-of-arrival and pulsewidth estimates for all received pulses over the full dynamic range of the receiver where pulsewidth and time-of-arrival are defined at the -6 dB points.

The resulting code, it should be noted, is <u>not</u> a cyclic code, in that not all cycled code words result in other code words. The code words are still generated by the same polynominal G(x), however, so all the encoding and decoding procedures still apply. Mathematically, whereas the natural cyclic code uses algebra based on modulo  $x^n-1$ , the shortened cyclic code uses algebra based on:

$$x^{n-i}$$

$F(x) = x^{n-i} - R(x), R(x) = remainder of ---- (2-12)$

$G(x)$

Thus, a shortened cyclic code is also known as a pseudo-cyclic code.

For Mode S, the message codes employ 24 parity bits, and are shortened to either a length of 56 or 112-bits depending upon whether a 32-bit or 88-bit message is being transmitted.

a) 1087 MHz

b)

1090 MHz

ALL PHOTOS: 0.5 µSEC/DIV. 8 dB/VERTICAL DIV.

c) 1093 MHz

Fig. 2.2-3. GATCAS receiver log video response.

For Mode S, b=24. Thus mathematically:

$$f = \frac{A(x) G(x)}{x^{24}} \text{ with remainder } \frac{r(x)}{-\frac{1}{x^{24}}} \text{ lost}$$

(3-2)

The actual uplink message can then be written as:

$$U = x^{24} M(x) + R(x) + \frac{A(x) G(x)}{x^{24}} + \frac{r(x)}{x^{24}}$$

message parity address function remainder

$$(- = +)$$

where, for review:

$$x^{24} M(x) = m(x) G(x) + R(x)$$

(3-4)

The transponder decoding procedure (to decode the address) is to multiply the received message by  $\mathbf{x}^{24}$  and then divide the result by  $G(\mathbf{x})$ :

$$U' = \frac{x^{24}}{G(x)}$$

(3-5)

If no errors were made in transmission, the result would be by (3-3) and (3-4):

$$U' = \frac{x^{24}}{G(x)} [m(x) G(x) + R(x) + R(x) + \frac{A(x) G(x)}{x^{24}} + \frac{r(x)}{x^{24}}]$$

$$= x^{24} m(x) + A(x) + \frac{r(x)}{G(x)}$$

$$= x^{24} m(x) + \frac{r(x)}{G(x)}$$

$$=$$

Thus the address will be directly readable as desired. If an error occurred:

Fig. 2.3-1. VPQ block diagram.

If step 1 indicates an error exists, the residual remainder after the address is removed is called the error syndrome. It is used to perform the step 2 and 3 operations as explained below.

Whenever an error is present, the syndrome will be non-zero. For a given 24-bit message segment, there are  $2^{24}$ -1 possible burst error patterns. Each of these patterns will produce a different one of the  $2^{24}$ -1 possible syndromes. Thus, there is a 1-to-1 correspondence between errors and syndromes. The syndrome pattern will differ from that of the error because of the division of the message by G(x) during the decoding process. The only time this pattern transformation does not occur is when the error burst is in the low-order 24-bits; in that case the syndrome and the error are identical.

of course, the burst error can occur in any 24-bit segment. Since the errors in each such segment can generate every possible syndrome, the mapping from syndromes to errors is many-to-one. A given syndrome is produced by different error patterns in different segments, however, as the transformation is a function of error location. The syndrome thus contains no information concerning the location of the error; an independent source is needed for that function. Once the position of the error is located, though, the syndrome will specify the error pattern.

Each received bit is decoded in the Mode S sensor as a 0 or 1, with a separate confidence bit produced as described in Chapter 1 to indicate the receiver's certainty as to its decision. High confidence bits are assumed to be correct, and are not permitted to be changed. If the error syndrome indicates a burst error, and some 24-bit segments of the message has a pattern of low confidence bits that matches the 1's in the transformed syndrome that applies to that segment, the error will be assumed to be located, and these bits will be corrected. Errors due to multiple bursts, or errors in high confidence bits, can not be corrected. Of course, infrequently a wrong correction will be performed.

The first decoding step is division of the received message by the generator polynomial. If no error has occurred, and using (3-11) and (3-4):

$$\frac{D}{G(x)} = \frac{x^{24}M(x)}{G(x)} + \frac{R(x)}{G(x)} + \frac{A(x)}{G(x)}$$

$$= \frac{m(x)G(x)}{G(x)} + \frac{R(x)}{G(x)} + \frac{R(x)}{G(x)} + \frac{A(x)}{G(x)}$$

$$= \frac{m(x)G(x)}{G(x)} + \frac{R(x)}{G(x)} + \frac{A(x)}{G(x)}$$

$$= \frac{m(x)G(x)}{G(x)} + \frac{A(x)}{G(x)}$$

(3-12)

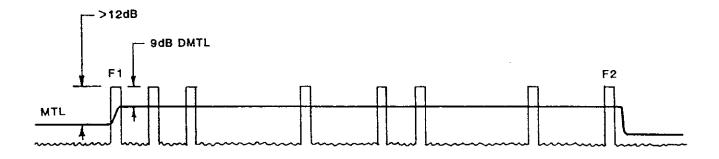

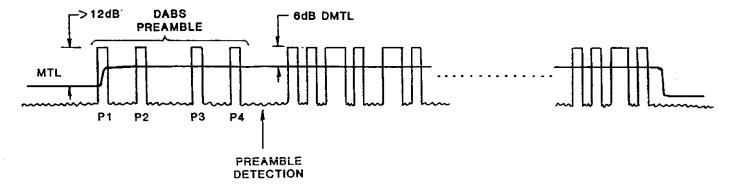

Fig. 2.3-3. ATCRBS DMTL.

DMTL = DYNAMIC MINIMUM TRIGGER LEVEL

Fig. 2.3-4. Mode S DMTL.

- 4. if all 1's in the syndrome are paired with a low confidence bit, the error has been located

- 5. else cyclically shift right the message and the confidence word

- return to 2, using the new shifted message as N(x)...

Fortunately, the need to perform the whole division process each time can be eliminated. This is because the syndrome  $S_1$  of the <u>left</u> cyclically shifted message can be produced directly from the original syndrome  $S_0$ . By definition of the syndrome, it is the remainder when dividing N(x) by the generator G(x):

$$S_0 = N(x) - G(x) Q_0(x)$$

(3-16)

where  $Q_0(x)$  is some quotient, and  $S_0$  is of degree 23 or less. The left shifted message's syndrome  $S_1$  is given by:

$$S_1 = xN(x) - G(x) Q_1(x)$$

(3-17)

where xN(x) is the left shifted message,  $Q_1(x)$  is a different quotient, and  $S_1$  is again of degree 23 or less. Then:

$$xS_0 = G(x) \{xQ_0(x) - Q_1(x)\}$$

(3-18)

But the degree of the left side is at most 24, while that of G(x) is exactly 24. Therefore the quantity in brackets must be a constant c (0 or 1) to keep the right side degree no greater than 24. Furthermore, if the degree of  $S_0$  is less than 23 (that is, if its leading coefficient  $s_{23}$ =0), then the left side is of degree 23 or less, requiring c to be 0. Otherwise, if  $s_{23}$ =1,  $x_0$  is of degree 24 while  $S_1$  is of degree 23 or less, so the left side cannot be zero, requiring c to be 1. Summarizing these results:

$$s_1 = xs_0$$

if  $s_{23} = 0$

$s_1 = xs_0 + G(x)$  if  $s_{23} = 1$  (3-19)

This equation states that the syndrome of the left shifted message can be obtained from the original syndrome by a shift and add the divisor operation. The process can be implemented by entering the original syndrome into a division circuit set to divide by G(x), of the type shown in Fig. 4.4, and operating the circuit with no input. Each cycle then shifts the syndrome, and adds G(x) or 0 according to whether the rightmost stage  $(s_{23})$  is 1 or 0 respectively, as required by (3-19).

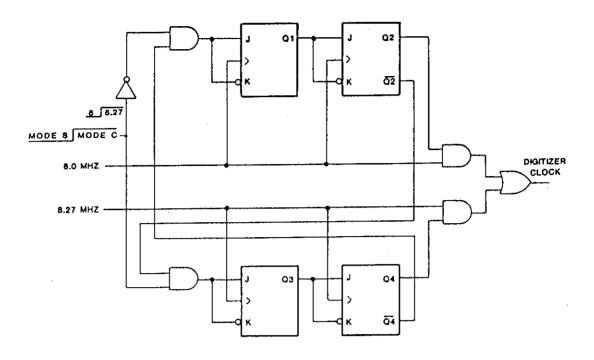

B) DIGITIZER CLOCK SWITCHING CONTROLLER

Fig. 2.4-1. Digitizer clock control.

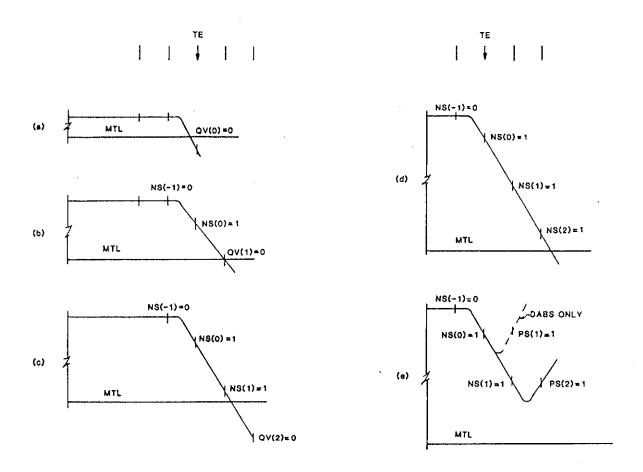

#### 4.0 POLYNOMIAL ARITHMETIC

As seen in the previous chapter, encoding and decoding procedures require numerous polynominal arithmetic operations: addition, multiplication, and division (subtraction is the same as addition, as +1 = -1 in modulo-2 arithmetic). Addition is implemented simply by a modulo-2 adder, also known as an exclusive-or circuit. Multiplication and division, however, require fairly complex shift register implementations. This chapter presents the details of these circuits.

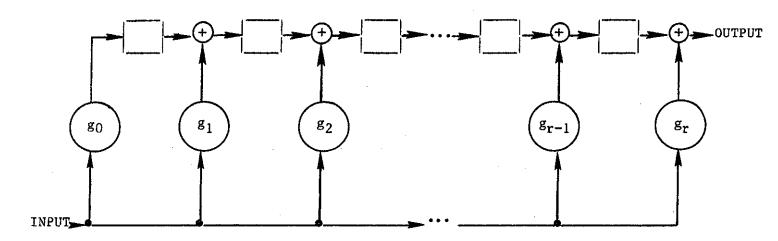

#### 4.1 Polynomial Multiplication

The product of two polynomials, P(x) = H(x) G(x), is formed by grouping together and summing modulo-2 all cross-coefficient terms having the same exponent sum. In particular, the product coefficient  $p_i$  is given by:

$$p_{j} = \sum_{i=0}^{r} g_{i}h_{j-i} \qquad (r \text{ the degree of G}) \qquad (4-1)$$

where

$$h_{j-i} = 0$$

for  $j-i < 0$

$h_{j-i} = 0$  for  $j-i > k$  (k the degree of H)

Thus, the product coefficient can be computed if all the g coefficients are available along with the r+1 h coefficients from  $h_1$  down through  $h_{1-r}$ .

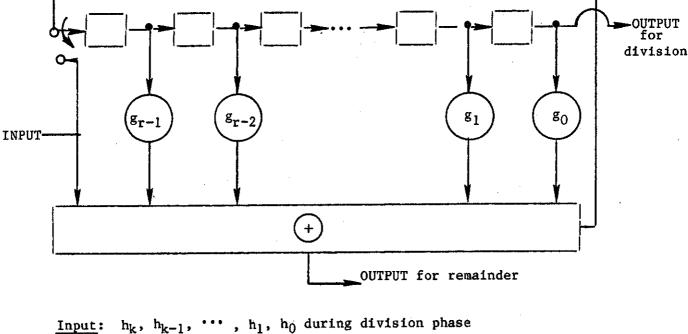

Figure 4-1 presents a tapped r-stage shift register circuit that implements this operation. The h coefficients are entered one by one, highest one first, into the register (initialized to all zeroes). After the last one  $(h_0)$  is entered, zeroes are fed in until the multiplication is completed. Thus the input plus the register always contains the sequence  $h_j$ ,  $h_{j-1}$ ,  $h_{j-r}$  as required, for all j from n=r+k to 0. The g coefficients are represented by the presence  $(g_1=1)$  or absence  $(g_1=0)$  of the inter-stage taps. Thus, each clock cycle, the summation box produces the product coefficient according to the above summation formula.

An alternate multiplication circuit is also commonly employed. This circuit, shown in Fig. 4-2, generates each product coefficient piece by piece as the input h coefficients are encountered. The above summation formula indicates that the coefficient  $h_i$  contributes to r+1 different product coefficients as follows:

$$h_i g_0 + p_i$$

$h_i g_1 + p_{i+1}$

$\vdots$

$h_i g_n + p_{i+n}$

Fig. 2.4-3. Trailing edge conditions.

## Multiply P(x) = H(x) G(x)

Input:  $h_k$ ,  $h_{k-1}$ ,  $\cdots$ ,  $h_1$ ,  $h_0$

## Register:

contains r partial product coefficients, each of which is generated one term at a time as they pass through the register stages.

$p_j$  is output when  $h_{j-r}$  is input

Fig. 4-2. Second multiplication circuit.

Fig. 2.4-5. Sliding window detector.

Divide Q(x) = H(x) / G(x)

$$x^{3} + x^{2} + 0 + 1$$

$$x^{4} + x^{2} + 1 | x^{7} + x^{6} + x^{5} + 0 + 0 + 0 + x + 1$$

$$x^{7} + 0 + x^{5} + 0 + x^{3}$$

$$x^{6} + 0 + 0 + x^{3} + 0 + x + 1$$

$$x^{6} + 0 + x^{4} + 0 + x^{2}$$

$$0 + x^{4} + x^{3} + x^{2} + x + 1$$

$$0 + 0 + 0 + 0$$

$$x^{4} + x^{3} + x^{2} + x + 1$$

$$0 + 0 + 0 + 0$$

$$x^{4} + x^{3} + x^{2} + x + 1$$

$$0 + 0 + 0 + 0$$

$$x^{4} + x^{3} + x^{2} + x + 1$$

$$0 + 0 + 0 + 0$$

$$x^{4} + x^{3} + x^{2} + x + 1$$

$$0 + 0 + 0 + 0$$

$$x^{4} + x^{3} + x^{2} + x + 1$$

$$0 + 0 + 0 + 0$$

$$1$$

Row A: Input Stream

B, D, F, H: feedback for Fig. 4-4 type divider

C, E, G: intermediate remainders

I: final remainder

Column L: shows formation of leading coefficient of remainder in Fig. 4-5 type divider

initial value (Row A) - given by input final value (Row G) - modified by prior quotient terms in rows B, D, F

Fig. 4-3. Sample division process.

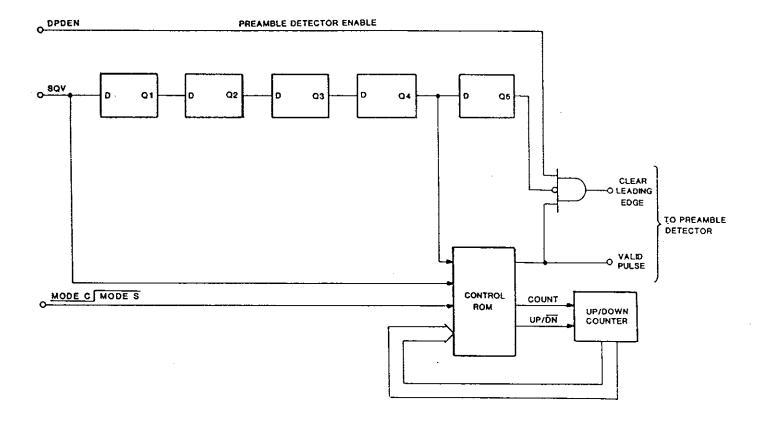

#### 2.4.5 Mode S Preamble Detector

The preamble detector is shown in Fig. 2.4-7. It is enabled when valid pulses are enabled at the sliding window detector (see section 2.4.4). Two D flip-flops spread the CLE signal to account for timing tolerances. Figure 2.4-6 shows pertinent timing. Note that the detection of a preamble starts the Reply and Interrogation Controller (RIC) processing a Mode S reply and any further interrupts while the message is being processed are ignored.

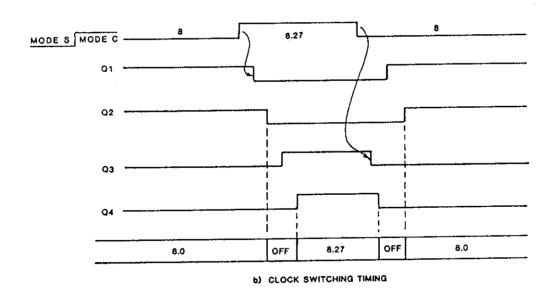

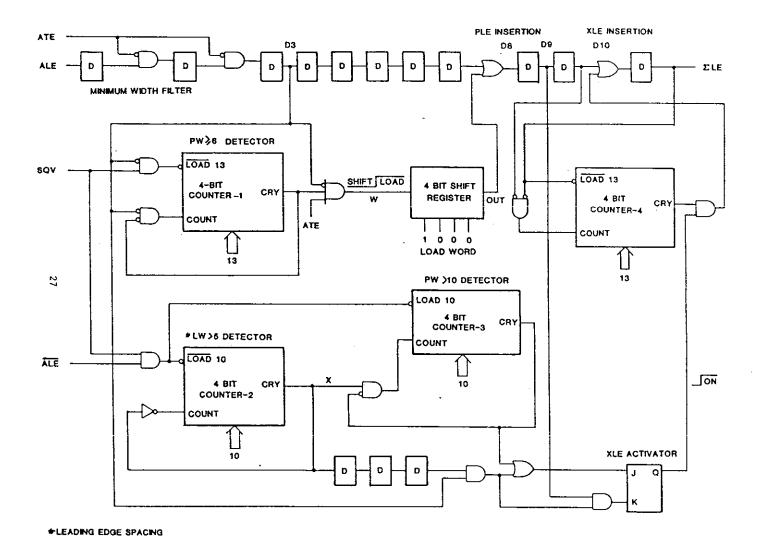

## 2.4.6 Pseudo Leading Edge Generation and Short Pulse Rejection

Overlapping ATCRBS replies will generate pulses having widths different than the standard code pulse width (3-5 samples at 120.6 nanoseconds per sample). To reject narrow pulses and to estimate the leading edge positions of pulses that have been combined in the TEU receiver, the logic shown in Fig. 2.4-8 is used.

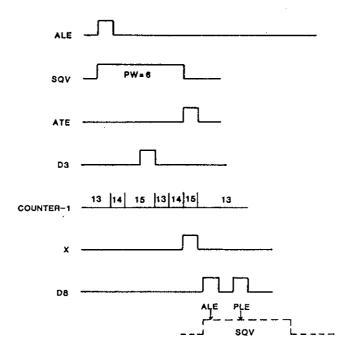

The first pulse processing step eliminates narrow pulses having widths less than three samples. Next, Counter I is used to artificially inject a pseudo leading edge four sample positions prior to the end of all pulses having widths greater than or equal to 6 (see figures 2.4-9, 2.4-10, and 2.4-11).

Finally, longer pulses are analyzed by the rest of the logic in Fig. 2.4-8 in order to insert extra leading edges every four samples starting at the leading edge of the pulse until the pseudo leading edge position is reached. The timing for a pulse having an 11 sample width is shown in Fig. 2.4-12.

A summary of the rules, adapted directly from the Mode S ground sensor design, for pseudo and extra leading edge generation is given below.

- (a) If PW = 1 or 2, then the leading edge shall not be represented in the leading edge data stream, but all other directly declared leading edges shall be represented in the leading edge data stream.

- (b) If PW > 6, then a pseudo-leading edge shall be declared at the sample time four sample intervals prior to the declared trailing edge.

- (c) If PW > 10, then additional pseudo-leading edges (called extra leading edges) shall be declared every fourth sample interval following the leading edge but prior to the pseudo-leading edge inserted in (b).

- (d) If LW > 5, then additional pseudo-leading edges shall be declared every fourth sample interval following the first leading edge but prior to the second leading edge.

Note that when a leading edge declaration is followed by a trailing edge declaration, PW is used to denote this pulse width in terms of sample intervals. LW is used to denote the spacing between two successively declared leading edges in terms of sample intervals.

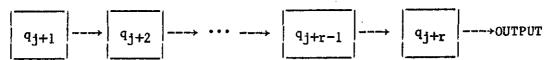

$q_{-1}$ ,  $q_{-2}$ , ...,  $q_{-r}$  during remainder phase

Register: as  $q_j$  is being generated (and  $q_{j+r}$  is being output)

final value: remainder quotients  $q_{-r} \xrightarrow{--} q_{-1}$ must be multiplied by G(x) to get remainder

thrown to disconnect feedback and connect input to produce Switch:

the multiplier needed to generate remainder

Feedback: new quotient coefficient

Fig. 4-5. Second division circuit.

Fig. 2.4-8. Pseudo and extra leading edge generators.

Using the facts that the low order H(x) terms are all zero, and that -=+, the final result is:

$$R(x) = Q(x) G(x)_{low-order}$$

(4-6)

Expanding this result:

$$R(x) = [q_0 g_{r-1} + q_1 g_{r-2} + \cdots + q_{r-1} g_0]x^{r-1}$$

$$+ [q_0 g_{r-2} + q_1 g_{r-3} + \cdots + q_{r-2}g_0]x^{r-2}$$

$$+ \cdots + [q_0 g_1 + q_1 g_0]x + q_0 g_0$$

$$(4-7)$$

At the time the last quotient  $q_0$  has been generated by the division circuit feedback, the register stages contain  $q_0$  through  $q_{r-1}$ . Furthermore,  $q_0$  is aligned with  $g_{r-1}$ ,  $q_1$  with  $g_{r-2}$ , etc. Thus the circuit, when placed in a multiplier configuration, will generate, sequentially, the remainder terms. The circuit in Fig. 4-6, therefore, implements both the required division and remainder generation operations. This second type of division circuit now requires no more cycles than the first to perform these operations.

Fig. 2.4-10. Pseudo leading edge generation, PW = 6.

Fig. 2.4-11. Pseudo leading edge generation, PW = 10.

#### 5.0 MODE S IMPLEMENTATION

Now that the mathematical description of the Mode S uplink and downlink coding processes has been developed (in Chapter 3), and the polynomial arithmetic circuits have been described (in Chapter 4), the actual Mode S sensor and transponder coding implementations can be provided. This chapter presents the actual figures contained in the Mode S National Standard and Specification (FAA-E-2716). Each figure is functionally explained by putting together the knowledge provided by the previous two chapters.

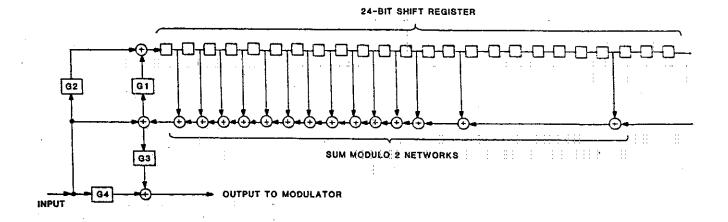

## 5.1 Uplink Implementation

The sensor uplink encoder is shown in Fig. 5-1. Basically, it is the revised division circuit presented earlier in Fig. 4-6. Note that the output is taken at the feedback loop, rather than 24 cycles later when this value exits the shift register as in the true division circuit of Fig. 4-5. This change is thus equivalent to multiplying the input by  $x^{24}$ , yielding the division  $x^{24}M(x)/G(x)$  as desired.

With the switch up, the division is performed, and the remainder quotient coefficients placed into the shift register as explained in the previous chapter. Then, when the switch is lowered to remove the feedback, two simultaneous operations occur in the now multiplier circuit (refer to Fig. 4-6). First, the remainder R(x) is generated in the manner explained in the last chapter when the input of the address is ignored. Second, the presence of this input through the switch causes it to be multiplied by G(x). This latter multiplication is not completed, however, as the 24 trailing zeroes needed to complete the formation of the product (see 4.1) are not input. Thus only the high-order bits are produced. The result, by superposition, is that the AP field output is:

$$AP = R(x) + A(x) G(x)_{high order}$$

(5-1)

as desired.

The transponder decoder circuit, also shown in Fig. 5-1, is again of the type of Fig. 4-6. Only this time, it is always left in the division mode. Once again, the input is multiplied by  $x^{24}$  due to the position of the output. Thus the result is:

$$U' = \frac{x^{24}}{G(x)} \tag{5-2}$$

as desired.

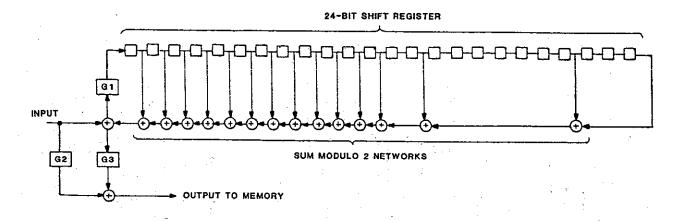

## 5.2 Downlink Implementation

The transponder encoder circuit, also shown in Fig. 5-1, is virtually identical to the sensor uplink encoder. The difference is that the address is not input to the multiplier circuit through the switch for the second part of

## 2.5 Reply and Interrogation Controller

## 2.5.1 General Description

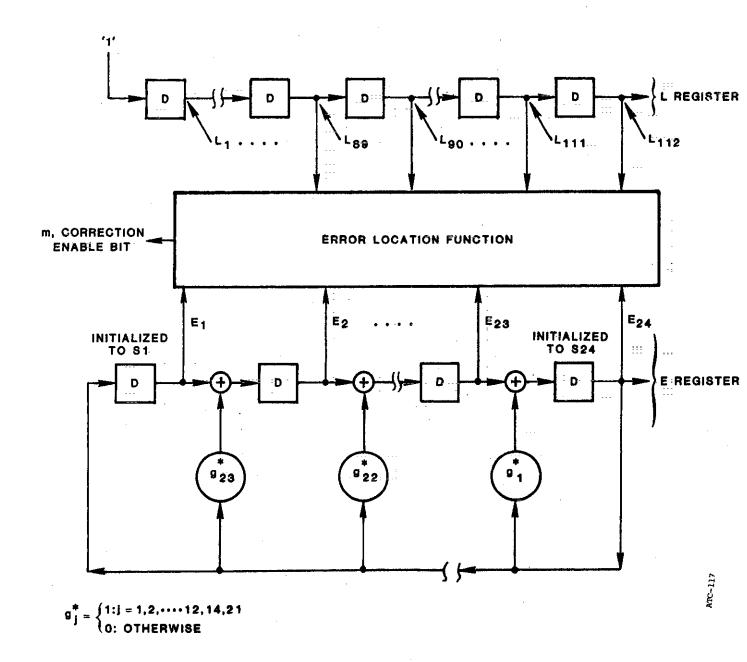

The Reply and Interrogation Controller (RIC) controls the processing of Mode S and ATCRBS interrogations and replies. Upon command from the Z8002 computer, the RIC initiates and coordinates the execution of one of nine predefined tasks. Upon completion of one of these tasks, the RIC interrupts the computer so the results can be retrieved and processed.

The RIC consists of an Am2910 microprogram sequencer, Am2914 interrupt controller, microprogram memory, control register, status register, range counter, and Mode S data memory. A block diagram of the RIC is shown in Fig. 2.5-1.

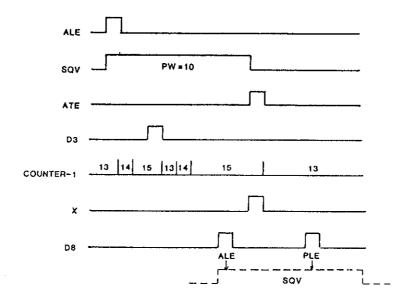

## 2.5.2 Am 2910 Microprogram Sequencer

The Am2910 is a bipolar microprogram controller intended for use in high-speed microprocessor applications [1]. Its internal architecture has a fixed-width, 12-bit, data path allowing for an address space of up to 4K words of microprogram. Figure 2.5-2 shows a block diagram of the internal architecture. The controller contains a four-input multiplexer that is used to select either the register/counter, microprogram counter, direct input, or stack, as the source of the next micro-instruction address.

The register/counter consists of 12 D-type, edge-triggered flip-flops, with a common clock enable. The data bus furnishes data for loading the register/counter.

The microprogram counter consists of a 12-bit incrementer followed by a 12-bit register. An external control to the incrementer allows the microprogram address to be incremented or to remain unmodified. If the microprogram address is not incremented, the same micro-instruction is executed any number of times. This feature is critical in properly synchronizing the signal processor to decode a Mode S reply.

The third source for the multiplexer is the direct (D) input. This is used when a branch is required to alter program flow.

The fourth input to the multiplexer is a 5-word by 12-bit stack. The stack is used to provide return address linkage when executing micro-subroutines or loops. The stack contains a built-in stack pointer (SP) which always points to the last file word written. The stack pointer operates as an up/down counter.

The internal parts of the Am2910 are controlled by the instruction programmable logic array (PLA) which is driven by control signals and instruction inputs from the microprogram memory and an external conditional input. The instruction executing the external conditional input to the Am2910

the operation. Thus, no multiplication of it by G(x) takes place. Instead, the input is merely added to the remainder being generated. Thus the AP field is now:

$$AP = R(x) + A(x)$$

(5-3)

as desired.

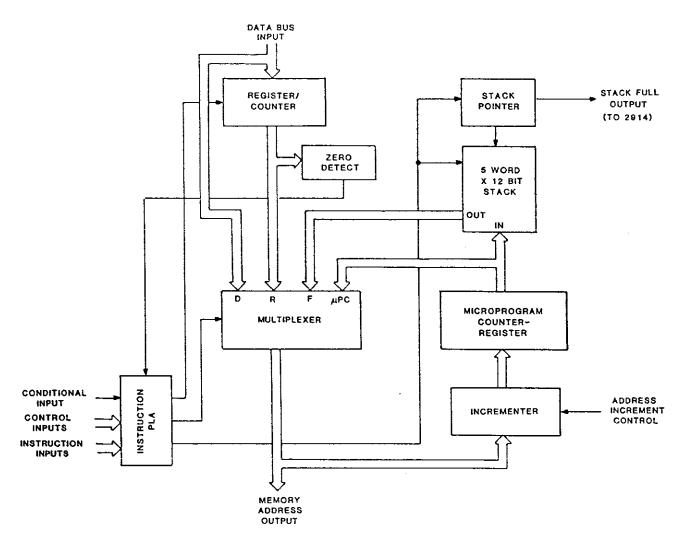

The sensor decoder represents the major hardware complexity of the coding system. Figures 5-2, 5-3, and 5-4, taken from the Mode S specification, highlight the implementation. First, as shown in Fig. 5-2, the downlink message is entered into the A-Register, which is a division circuit of the type of Fig. 4-4. This circuit produces the remainder in parallel-readable form in the shift register. Thus, the remainder can be bit-by-bit added (compared) to the expected address to produce the error syndrome. Meanwhile, the message and confidence bits are being stored in the DB and CB registers respectively. The confidence test shown in the figure is discussed below.

If the syndrome is non-zero, an error burst is present. This burst can be in any 24-bit segment of the message. To produce the sequence of successively cyclic shifted syndrome patterns, the "reverse division" E-Register circuit of Fig. 5-3 is used. This circuit, as explained in Section 3.2, is filled by the initial syndrome in bit reversed order, and its taps implement the reciprocal polynomial G'(x) (compare the g coefficient order with Fig. 5-2). The explanation also indicated, as shown, that it has no input, only feedback. The CB and DB registers are transerred to the L and M registers respectively, also in reverse order, so that the low-order 24-bits are the first set to be checked.

One shift at a time, the successively cycled syndrome is produced according to equation (3-19). In parallel, the message and confidence stream are cycled one-bit at a time. When the l's of the syndrome pattern match the low confidence l's in the low order 24-bits of the confidence bit pattern, the error has been trapped. The correction enable bit is then set by the error location function.

At this time, as shown in Fig. 5-4, the feedback of the E-Register is disabled, so that the syndrome can be read out serially. In parallel, the M register shifts out the message bits. Each bit corresponding to a l in the error syndrome is then corrected by adding the two streams bit-by-bit.

One further check is made during the detection phase of the correction process, namely the number of low confidence bits contained in each 24-bit segment of the message is determined. If the number of them ever exceeds a threshold, error correction is rejected. This is because the possibility of an erroneous correction goes up sharply with the number of low confidence bits. In the limit, if any 24 consecutive bits were low confidence, the syndrome pattern would be matched no matter what it was, and correction of those specific 24 bits would always occur.

Fig. 2.5-2. Block diagram of AM2910.

FIG. 5-3. ERROR LOCATION LOGIC

Any combination of these inputs can be enabled or disabled by using the masking feature of the Am2914.

### 2.5.4 Microprogram Memory

The microprogram memory contains all the microprogram firmware necessary to the execute the 5 predefined collision avoidance tasks and 4 diagnostic tasks. The memory is designed for a maximum size of 2K words with a word being 88 bits wide. Of the 88 bits in a word, 86 bits are defined and 2 bits are undefined and available for future use. Figure 2.5-3 shows the field definition for the 88 bit microprogram word. All 9 tasks require a total of 325 words of memory and are located in the first 625 words of the address space. The memory is built using Am27s181 bipolar PROMs which provide high speed access enabling the signal processing to run at the required speed.

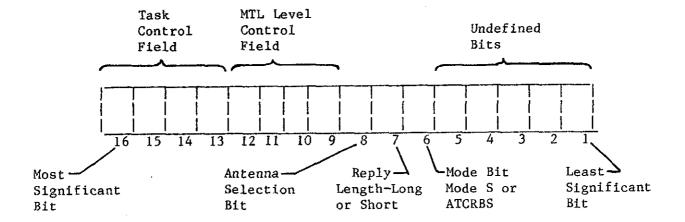

#### 2.5.5 Control Register

In order for the Z8002 computer to communicate with the RIC, a control register (see Fig. 2.5-1) is provided which the computer can load with the required control information prior to starting a particular task. The control register is 16 bits wide and is located at locations 512 and 513 in the Z8002 special I/O address space. Eleven of the bits in the register are defined and five are undefined and are available for future use. Figure 2.5-4 shows the control register field definition.

The four most significant bits (bits 13 through 16) of the control register represent the task control field which specifies what task the RIC is to perform next. Nine of the sixteen possible tasks have been defined and are listed in Fig. 2.5-5.

The 4 bit MTL control field (bits 8 through 12) allows the Z8002 computer to dynamically set the receiver sensitivity. This field controls the minimum threshold over the range -72 dBm to -40 dBm in 2 dB increments. All zeroes in the MTL field represent -72 dBm while all ones represent -40 dBm.

Three single bit fields are also contained in the control register. The first bit (bit 8) selects the antenna to be used in the present task. A l in this position selects the upper antenna and a 0 selects the bottom antenna.

The second bit (bit 7) sets the length of the expected Mode S reply in response to the last Mode S interrogation. A l in this bit indicates a long reply is expected and a 0 indicates a short reply is expected.

The last active bit (bit 6) in the control register represents the mode (Mode S or Mode C) of the current task. A l represents the Mode C mode and a 0 represents the Mode S mode.

The least significant five bits of the control register are undefined.

## REFERENCES

- 1. J. Barrows, "DABS Uplink Coding", ATC-49, Lincoln Laboratory, M.I.T. (25 July 1975).

- 2. J. Barrows, "DABS Downlink Coding", ATC-48, Lincoln Laborarory, M.I.T. (12 December 1975).

- 3. W. W. Peterson and C. J. Weldon, Jr., "Error Correcting Codes," Sec. Ed., M.I.T. Press, Cambridge, MA 1972).

- 4. T. Kasami and S. Matoba, "Some Efficient Shortened Cyclic Codes for Burst-Error Correction, "IEEE Trans. Inf. Theory <u>IT-10</u>, 252 (1964).

Fig. 2.5-4. RIC control register field description.

```

0000 - Mode C With No P4 Pulse

0001 - Mode C With P4 Pulse

0010 - Short Mode S Interrogtion

0011 - Long Mode S Interrogation

0100 - Squitter Listening

0101 - Undefined

0110 - ATCRBS Diagnostic #1

0111 - ATCRGS Diagnostic #2

1000 - Mode S Diagnostic #1

1001 - Mode S Diagnosite #2

1010 - Undefined

1011 - Undefined

1100 - Undefined

1101 - Undefined

1110 - Undefined

1111 - Undefined

```

Fig. 2.5-5. RIC task control field assignments.

5115

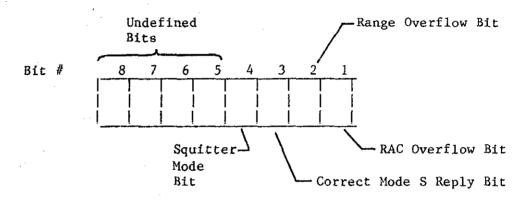

## 2.5.6 Status Register

To allow the Z8002 computer to monitor RIC operation, an 8-bit status register is provided which can be accessed by reading location 516 in the Z8002 special I/O address space. The least significant four bits have been defined while the most significant four bits are undefined and are available for future expansion. Figure 2.5-6 shows the status register bit definitions. When the least significant bit is set, the reply address counter (RAC) has rolled over meaning that an excessive number of squitters or Mode S replies have been received. If the second bit is set, the range counter has reached its maximum and rolled over. When a Mode S interrogation is sent out and none of the replies received are correct, the 3rd bit in the status register is set. The fourth bit in the status register is used to indicate when the RIC is in the squitter mode. This bit is set when the squitter mode is entered and cleared when exiting the squitter mode.

# 2.5.7 Range Counter Latch

The RIC unit has a 10-bit range counter which is used in the Mode S mode operation. The counter is clocked at 8 MHz allowing for a maximum range window of 8.7 miles. A latch is connected to the counter which latches the range when a preamble is detected. The latch can then be accessed by reading locations 518 and 519 in the Z8002 special I/O space. When the miximum range is reached the counter halts and a bit in the status register is set.

## 2.5.8 Mode S Data Memory