# On Chip Nonlinear Digital Compensation for RF Receiver

Karen M. G. V. Gettings, Andrew K. Bolstad, Show-Yah Stuart Chen, Benjamin A. Miller and Michael Vai

#### HPEC 2011

This work is sponsored by the Department of the Air Force under Air Force contract FA8721-05-C-0002. Opinions, interpretations, conclusions and recommendations are those of the author and are not necessarily endorsed by the United States Government.

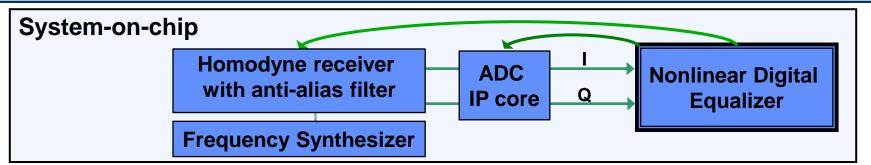

### **System On Chip Equalization**

- We designed a nonlinear digital compensation circuitry that is part of a System On Chip (SOC) design

- SOC implementations are an attractive solution for SWaP restricted applications, partly because of targeted design needs

- We exploit the benefits of SOC implementations by co-designing the analog hardware and digital processing

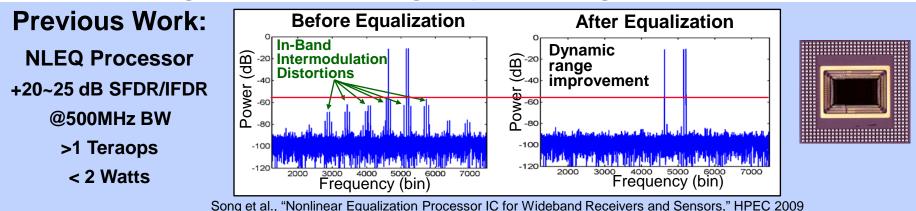

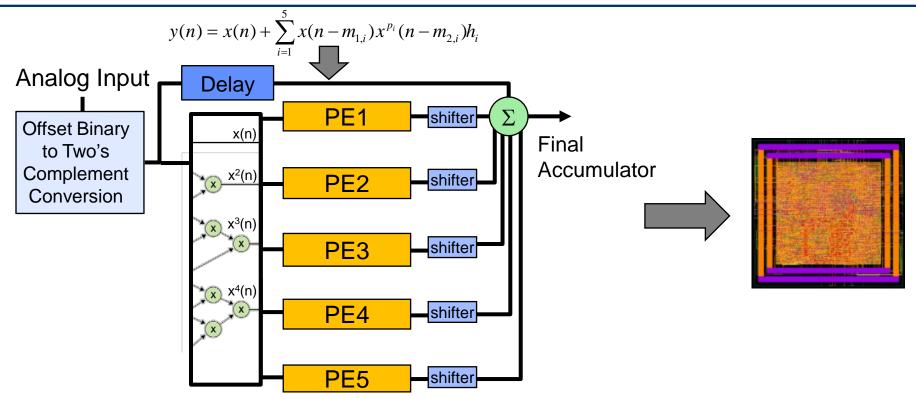

## **Nonlinear Digital Equalizer Design**

- Established a low-power standard-cell synthesis design flow – IBM 65 nm CMOS process

- Created an overall compensation architecture customized for our current front end system

- Design is optimized to minimize power consumption

1951–2011 LINCOLN LABORATORY MASSACHUSETTS INSTITUTE OF TECHNOLOGY

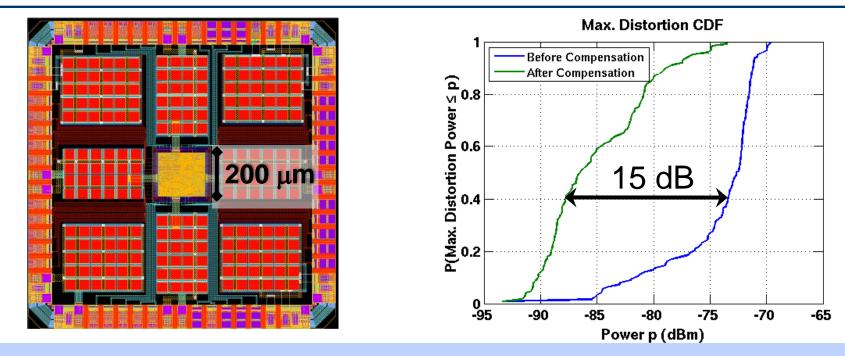

#### **Projected Design Performance**

- The digital compensation architecture has been synthesized, placed, routed and taped-out

- Core size: 200 μm by 200 μm

- Simulation results show:

Approximately 10 mW of power at 200 MHz

**Compensation of front end filter:**

15 dB improvement for median dynamic range