#### Impact on High-Performance Applications: FPGA Chip Bandwidth at 40 nm

J. Ryan Kenny Altera Corporation 101 Innovation Drive San Jose, CA 95134

High-Performance Embedded Computing Workshop 23-25 September 2008

© 2008 Altera Corporation—Public

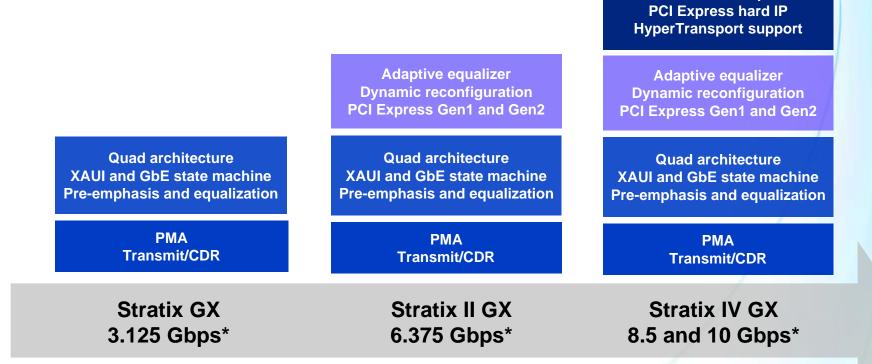

### **Best-in-Class Transceiver Lineage**

# The same analog design team improving the transceiver block through successive generations

#### Building on a solid foundation lowers risk

#### \* All transceivers operate down to 640 Mbps

© 2008 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

8.5 and 10 Gbps

2

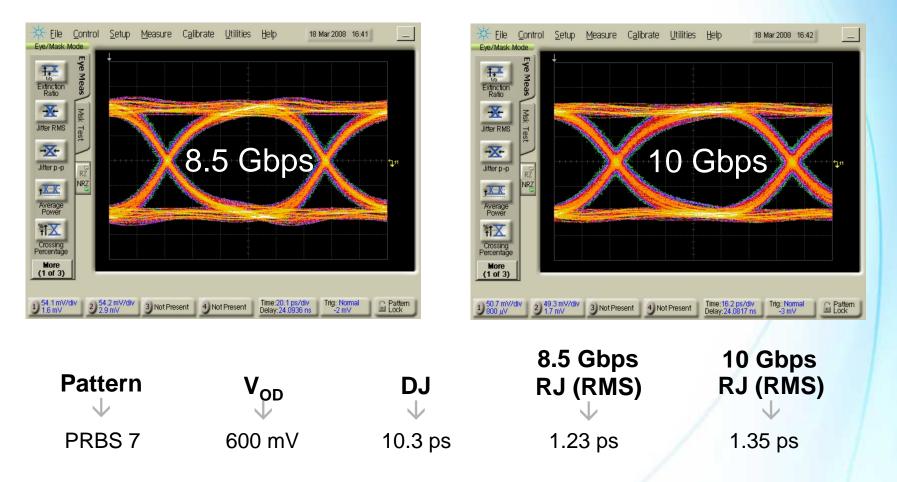

#### **40-nm Transceiver Eye and Jitter Test Set Up**

| Conditions                          | $V_{OD} = 0.6 V$<br>Nominal voltages: $V_{CCHX} = 3.0 V$ ,<br>$V_{CCHTX} = 1.4 V$<br>$V_{CCLX} = 1.1 V$<br>Temperature: 25°C<br>6.375 Gbps, 8.5 Gbps, and 10 Gbps/on chip PRBS7 |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conditions                          | V <sub>CCHTX</sub> = 1.4 V<br>V <sub>CCLX</sub> = 1.1 V<br>Temperature: 25°C<br>6.375 Gbps, 8.5 Gbps, and 10 Gbps/on chip PRBS7                                                 |

| Agilent 81134A<br>Pattern Generator |                                                                                                                                                                                 |

| Pattern Generator                   |                                                                                                                                                                                 |

| trigger                             |                                                                                                                                                                                 |

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

#### 40-nm Transceiver Eye Diagram at 8.5 and 10 Gbps

#### **Extraordinary jitter performance**

© 2008 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

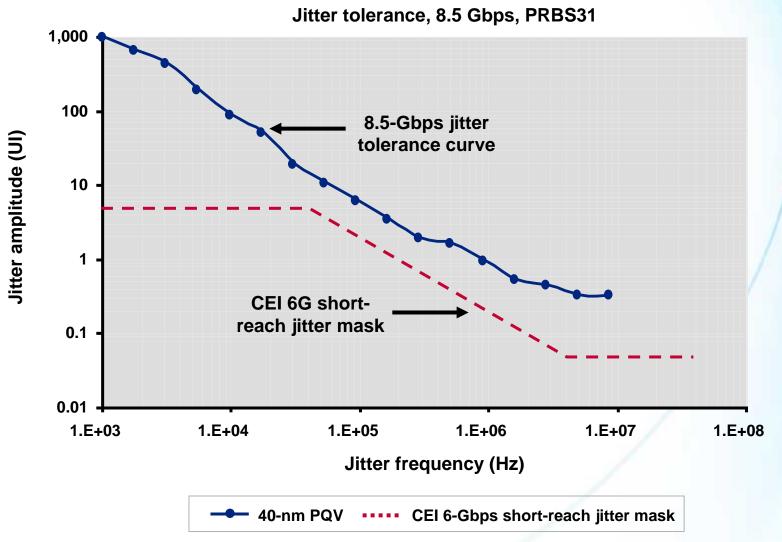

### **Jitter Tolerance at 8.5 Gbps**

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

## **High-Performance Applications**

In excess of 100 Gbps

(Mixture of 8.5 Gbps and 3.125 Gbps)

#### Chip-to-backplane

- As many as 48 lanes

- 24 up to 8.5 Gbps

© 2008 Altera Corporation—**Public** Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation