# SmartCell: Architecture, Design and Performance Analysis for Reconfigurable Embedded Computing

Xinming Huang

Embedded Computing Lab

Worcester Polytechnic Institute

http://computing.wpi.edu

Twelfth Annual HPEC Workshop September 23-25, 2008 MIT Lincoln Laboratory

## SmartCell: Tiled Architecture, Processor Design and Interconnect

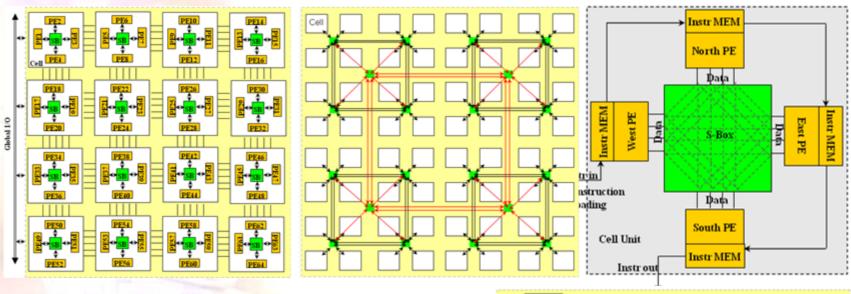

- Many cells are titled in 2D layout

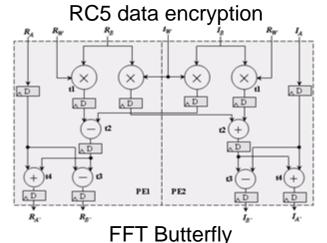

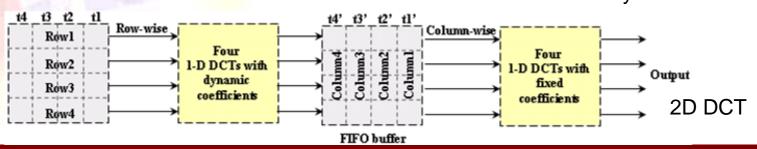

- Each cell has 4 PEs (N,W,S,E)

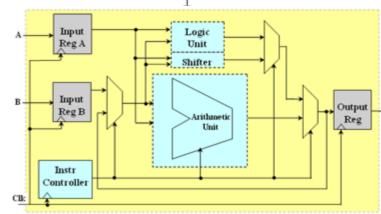

- Simplified processor with mem

- A crossbar within the cell; onchip interconnect uses CMesh

### Features and Application Domain

### System Design and Performance

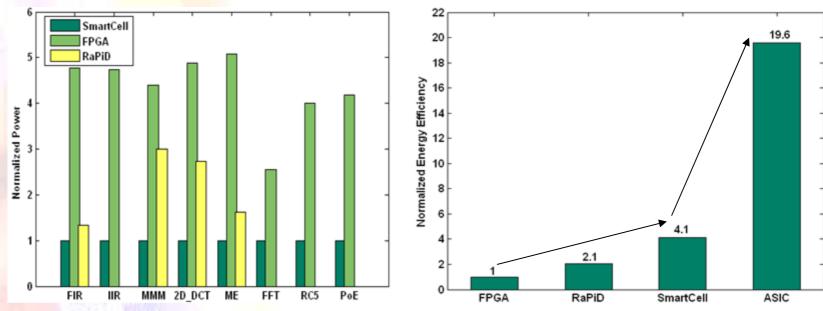

- Prototype chip design: 4x4 cells (64 PEs), .13 TSMC,

8.2mm², 1V, about 156mW @100MHz

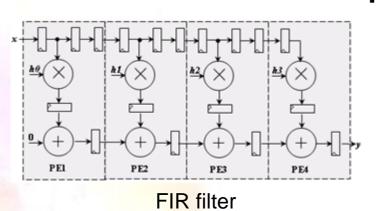

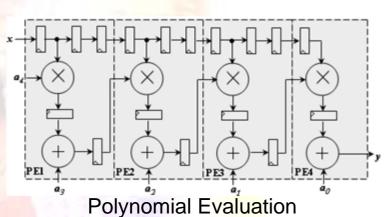

- Benchmark with RaPiD, Stratix-II (90nm), and ASIC

#### **Acknowledgement:**

- Dr. Michael Fritz, DARPA/MTO YFA Program

- Cao Liang, WPI graduate assistant, now with AMD