# Designing Processing Architectures for Space Applications

John Holland & Eliot Glaser Northrop Grumman Corporation P.O. Box 1693 Baltimore, Maryland 21203 john.holland@ngc.com

High Performance Embedded Computing (HPEC) Workshop 23–25 September 2008

## Space Applications Present Conflicting Design Challenges

Approved for public release; distribution is unlimited.

- Challenging Form Factor Requirements Constrain the Processing Design

- Environmental

- Thermal

- Packaging

- Material restrictions

- Size, weight, and power (SWAP)

- Processing Requirements Drive Technology Selection

- Memories

- CPUs

- Field programmable gate arrays (FPGA)

- Application specific integrated circuits (ASIC)

- High I/O packaging

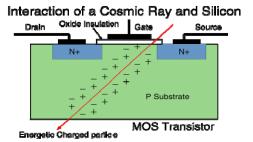

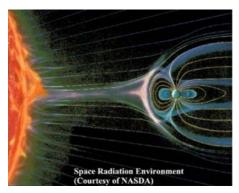

Radiation Variation with Orbit due to the Earth's Magnetic Field

## Form Factor Requirements for Space

Environment and Radiation

- Total dose radiation and single event effects (SEE)

- Launch vibration, vacuum & outgassing, material selection

- Thermal Management Cooling and Heating

- Adequate cooling path for hot components

- Minimize cold excursions

- Limited to conduction cooling and heat radiation

Approved for public release; distribution is unlimited.

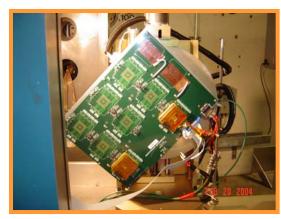

Component Radiation Testing

### Packaging

- Thermal cycling limited by CTE mismatches between components and boards

- Shielding must be considered at component, assembly, and subsystem levels

- Good system grounding is essential

- Size, Weight, and Power (SWAP)

- Power is critical and impacts size and weight

- Launch weight is expensive

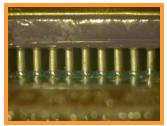

After 1500 Thermal Cycles

## Processing Requirements Demand Advanced Technology

#### Memories

- Radiation hardened SRAM and EEPROM are available

- Commercial DRAM and Flash NVM are denser and faster but require SEE mitigation

#### FPGAs

- Anti-fuse FPGAs are radiation hardened

- Flash-based and RAM-based FPGAs require multiple SEE mitigation techniques

#### ASICs

- Radiation-hardened fabrication processes available

- Non-rad-hard processes are more numerous, less expensive, and have more advanced feature sizes

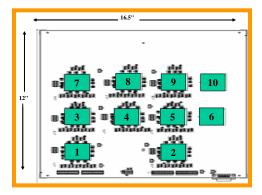

### High I/O Packaging

Ball Grid Array (BGA) and thin-shrink small outline (TSSOP) packages are susceptible to thermal cycle damage Approved for public release; distribution is unlimited.

High Speed ASIC Device

BGA Daisy-chain Package for CTE Testing

### In the Poster Session

- Radiation -- Total Dose, Single Event Effects

- Requirements, assessment, testing

- Thermal Considerations and Packaging Options

- Use of Memories in Space Applications

- Error detection and correction (EDAC) and power control

- FPGAs

- Anti-fuse, flash-based, and RAM-based

- Triple module redundancy (TMR), memory checking, and memory scrubbing

- ASICs

- Radiation hardened fabrication or upscreening & testing

- High IO Packaging Thermal Cycle Testing

Approved for public release; distribution is unlimited.

With risk assessment and risk mitigation, advanced processing technologies can be available for open system architectures.