# Multicore Acceleration of the Complex Ambiguity Function

D.P. Enright, E.M. Dashofy, M. AuYeung, R.S. Boughton, J.M. Clark, and R. Scrofano, Jr.

The Aerospace Corporation 2350 E. El Segundo Blvd. El Segundo, CA 90245-4691

### High Performance Embedded Computing (HPEC) Workshop

### 23-25 September 2008

DISTRIBUTION STATEMENT: Approved for public release; distribution is unlimited.

# Multicore Acceleration of the Complex Ambiguity Function

D.P. Enright, E.M. Dashofy, M. AuYeung, R.S. Boughton, J.M. Clark, and R. Scrofano, Jr.

- Performed Multicore Parallelization Study of the Complex Ambiguity Function (CAF)

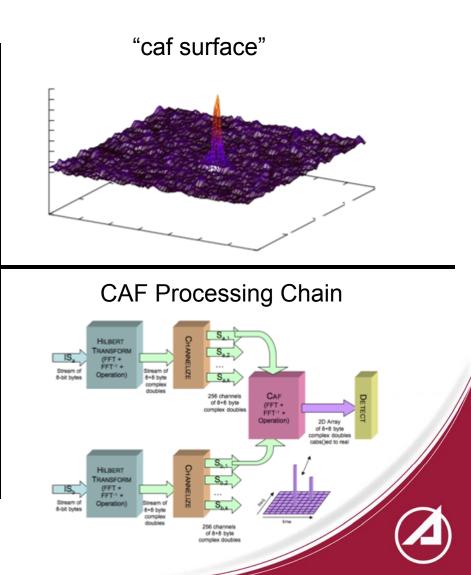

- CAF is a key algorithm for performing time and frequency delay of arrival (TDOA/FDOA) for actively sensed objects

- Output is "caf surfaces"

- Peak detection gives TDOA/FDOA

- Entire CAF evaluation requires pre-/postprocessing steps

- CAF module is most computationally intensive

- OpenMP loop-level parallelization strategy employed

- Parallel speedups of 75% or greater for dual-quad core Intel Xeon system

# **Computational Kernels & Parallelization Strategy**

- Four Modules

- Pre-/Post-processing: HILBERTTRANSFORM, CHANNELIZE, DETECT

- Computational Kernels: Multiple independent FFTs, FIR filters

- CAF: Computationally most intensive

- Computational Kernel: Multiple independent cross-correlations utilizing FFTs

$$A_{k}(m,\nu) = \sum_{l=0}^{L-1} S_{a,k}(l+\nu) \times S_{b,k}^{*}(l) \times e^{-j2\pi m l/L}$$

caf surface  $A_{k}(m,\nu)$

- Parallelization Strategy

- Large amounts of loop-level parallelism with multiple FFTs performed in parallel and no data-dependencies between loop iterations within HILBERTTRANSFORM and Снапления modules

- Ideal loop-structure for OpenMP omp parallel for iterative workshare construct

- CAF and DETECT modules enclosed by doubly-nested outer for-loop with multiple large FFTs performed in parallel and no data-dependencies between loop iterations

- Ideal loop-structure for OpenMP omp parallel for iterative workshare construct

# Workload-Driven Evaluation

- To assess efficacy of parallelization effort and the parallel scalability of the dualquad core system

- Workload was parameterized

- Scaling input size from 6.25 MS to 31.25 MS in steps of 6.25 MS (1MS = 2<sup>20</sup> samples)

- Observed linear-scaling in uni-processor runtime

- Processing a Nominal Surface case, i.e. culled number of caf surfaces, and All Surface case, i.e. all possible caf surfaces

- Two Workload-Driven metrics calculated

- Workload-Constrained (WC) metric

- Ability of parallel system to minimize overall wall-clock time

Speedup<sub>WC</sub>(*p* cores) =  $\frac{\text{Time}(1 \text{ core})}{\text{Time}(p \text{ cores})}$

- Modified Linear-Scaled Workload Time-Constrained (MLSWTC) metric

- Ability of parallel system to maintain a uni-core runtime as workload is increased in proportion to number of parallel resouces (cores)

Speedup<sub>MLSWTC</sub>(*p* cores, min(*p*,*ubism*) input size) =  $\frac{\text{Time}(1 \text{ core, } 1 \text{ input size})}{\text{Time}(p \text{ cores, min}(p, ubism) \text{ input size})}$

- ubism is the upper-bound input size multiple of base input size (5 for study)

- Modification of "scaled-speedup" model of Gustafson[1]

[1] Gustafson, J.L., "Reevaluating Amdahl's Law", Comm. ACM, v. 31, no. 5, p. 532-533 (1988)

## Results

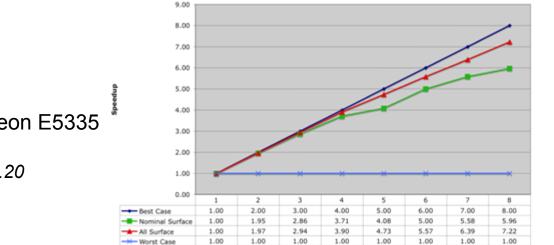

#### WC Speedup (6.25MS, -10dB) + (ICC+MKL)

Number of Cores

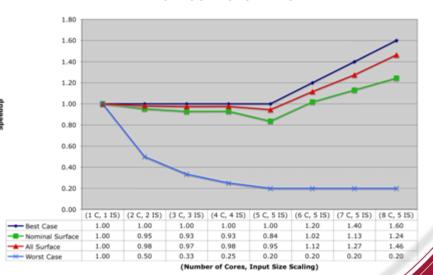

MLSWTC Speedup (-10dB) + (ICC+MKL)

- Using dual-quad core Intel Xeon E5335 "Clovertown" system<sup>1</sup>

- ICC v. 10.0 + MKL v. 10.0.3.20

- WC Speedup

- (6.25MS, -10dB) Workload

- (-10dB = 8K element CAF FFTs)

- Nominal Surface, 5.96/8 = 75%

- All Surface, 7.22/8 = 90%

- Process given workload 6x to 7.2x faster

- MLSWTC Speedup (-10dB)

- (5 cores, 5 input size)

- Nominal Surface, .84/1

- All Surface, .95/1

- Both Surface Processing Cases

- Process 5x base input with 6 cores in same amount of time as uni-core processor base input runtime

<sup>1</sup>2.0GHz; 2x4MB shared L2, 32KB I/D L1; 10.6 GB/sec FSB; 8GB system memory; 64-bit CentOS5