## GENERAL DYNAMICS Advanced Information Systems

### Implementation of Parallel Processing Techniques on Graphical Processing Units

Poster C.4

Brad Baker, Wayne Haney, Dr. Charles Choi

#### **Industry Direction**

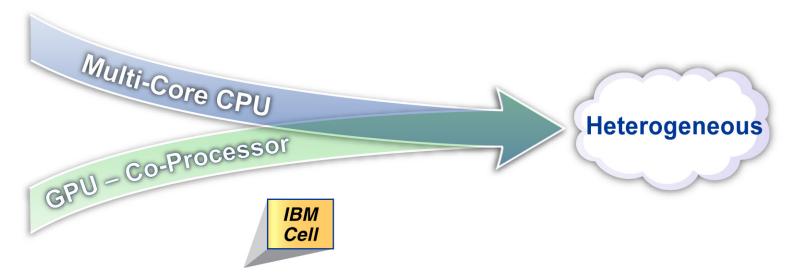

High performance COTS computing is moving to multi-core and heterogeneous silicon

#### **MULTI-CORE CPU**

- Multi-core CPU with smaller individual cores

- GPU co-processor

#### **CURRENT**

- Multi-core CPU with 1-3GPU co-processors

- Heterogeneous multi-core (IBM Cell)

#### **FUTURE**

Smaller, heterogeneous cores on same silicon

### Math Benchmark and Signal Processing String Results

| Fundamental Math Benchmarks |                       |                         |

|-----------------------------|-----------------------|-------------------------|

| Software Platform (GPU)     | 1k<br>SGEMM<br>Gflops | 1k 1d<br>Complex<br>FFT |

| Peakstream (AMD r520)       | 80.13                 | 8.7                     |

| CUDA (Nvidia g80)           | 95                    | 43.4                    |

| RapidMind (Nvidia g80)      | 24                    | 7.5                     |

| RapidMind (AMD r520)        | 26                    | 4.9                     |

| Intel Core 2 Quad QX6700    | 12                    | 14.2                    |

| AMD Opteron 265HE           | 8.8                   | 4.8                     |

#### **Nvidia Cuda Platform**

- Utilizes most powerful GPU on market

- Most extensive pre-built math library

Approx. 50%

Performance Gain

Using CUDA's FFT

# Application Results Architecture Execution Time VSIPL++ PNB Algorithm on Intel 735.78 msec

CUDA Batch Style PNB Algorithm on Nvidia g80 GPU

Core 2 Quad QX6700 CPU

367.23 msec

## GENERAL DYNAMICS Advanced Information Systems

### Implementation of Parallel Processing Techniques on Graphical Processing Units

Poster C.4

Brad Baker, Wayne Haney, Dr. Charles Choi