## Prototyping Advanced Military Sensor Systems Using FPGA-to-ASIC Design Flow

#### J Ryan Kenny

ADERA.

Jeff Wills Altera Corporation 101 Innovation Drive San Jose, CA 95134

### Rick Pancoast

Ellis Taliaferro Lockheed Martin MS2 199 Borton Landing Road Moorestown, NJ 08057

#### High Performance Embedded Computing Workshop

18-20 September 2007

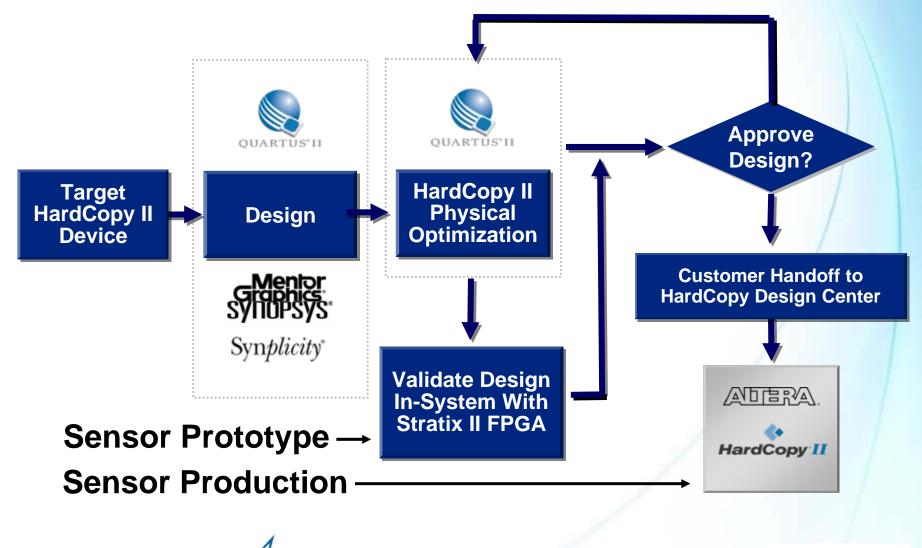

## FPGA to HardCopy ASIC Device Design Flow

LOCKHEED MARTIN

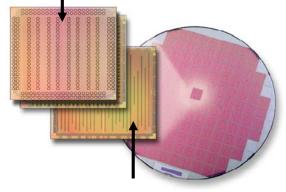

# Hard Copy ASIC Device – What

- True Structured ASIC

- Only Top Layers Custom

- FPGA Architecture with ASIC Routing

**Structured ASIC:** Customization Through Top Layers

Base Layer

- Flexibility of FPGA Design with Cost and SWaP Features of ASIC

- Reduce:

- Power by 50-70% (over FPGA)

- Design time from 52 Weeks (ASIC) to 20 Weeks (Hard Copy)

- Unit Cost after NRE estimated of \$350,000

- Risk virtually zero risk conversion

- Size by 60-85%

- Can be same pinout

- Up to 50% Performance Improvement

LOCKHEED MARTIN

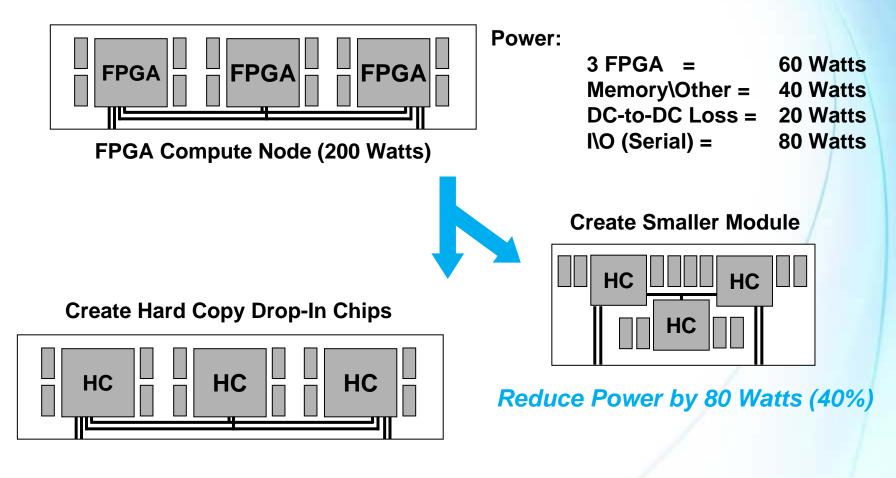

### **Compute Node** (Notional Architecture)

Reduce Power by 40 Watts (20%)