# Focus 3: Cell

#### Sharon Sacco / MIT Lincoln Laboratory

**HPEC Workshop**

19 September 2007

This work is sponsored by the Department of the Air Force under Air Force contract FA8721-050C-0002. Opinions, interpretations, conclusions and recommendations are those of the author and not necessarily endorse by the United States Government.

**MIT Lincoln Laboratory**

HPEC-1 SMHS 12/12/2007

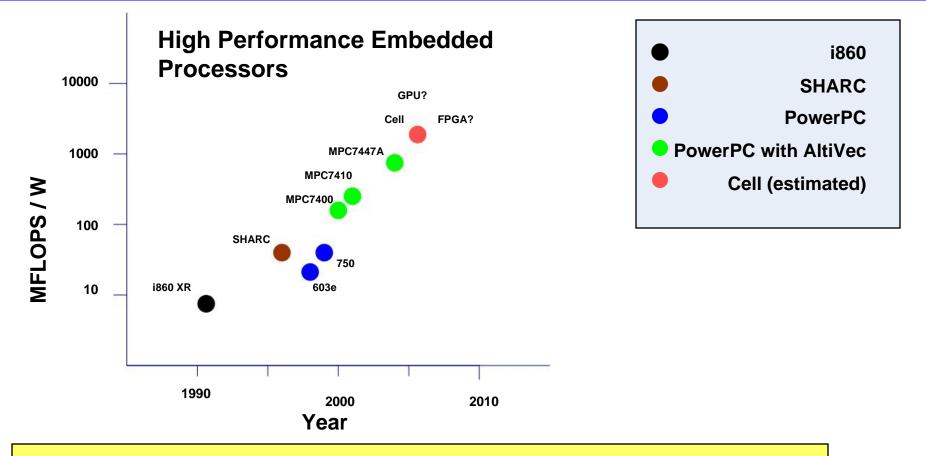

# **Embedded Processor Evolution**

- 20 years of exponential growth in FLOPS / W

- Requires switching architectures every ~5 years

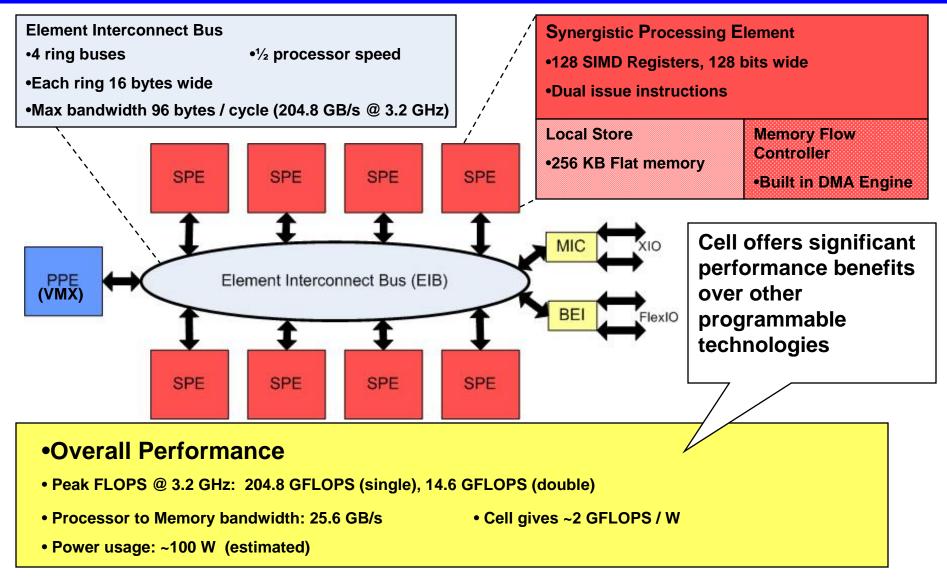

- Cell Processor is current high performance architecture

## **Cell Features**

- FFTC: Fastest Fourier Transform for the IBM Cell Broadband Engine

- Virat Agarwal, Georgia Institute of Technology

- Implementation of SIGINT Application on Cell-BE

- Richard Besler, Black River Systems Company

- Performance of a Multicore Matrix Multiplication Library

- Robert Cooper, Mercury Computer Systems

#### Wednesday:

- Session 4: Novel Applications

- Projective Transform on Cell: A Case Study

### Thursday:

- Session 5: Multicore Environments

- High Performance Simulations of Electrochemical Models on the Cell Broadband Engine

- Sourcery VSIPL++ for the Cell/B.E.

- Programming Examples that Expose Efficiency Issues for the Cell Broadband Engine Architecture

- PVTOL: A High-Level Signal Processing Library for Multicore Processors

- Focus 5: Benchmarking

- Exploring Multi-core Processors with Realistic Signal- and Imageprocessing Application Benchmarks

- Poster / Demo C: Cell / GPU Technologies

- Session 6: Awards Session

- Implementation of Polar Format SAT Image Formation on the Cell Broadband Engine