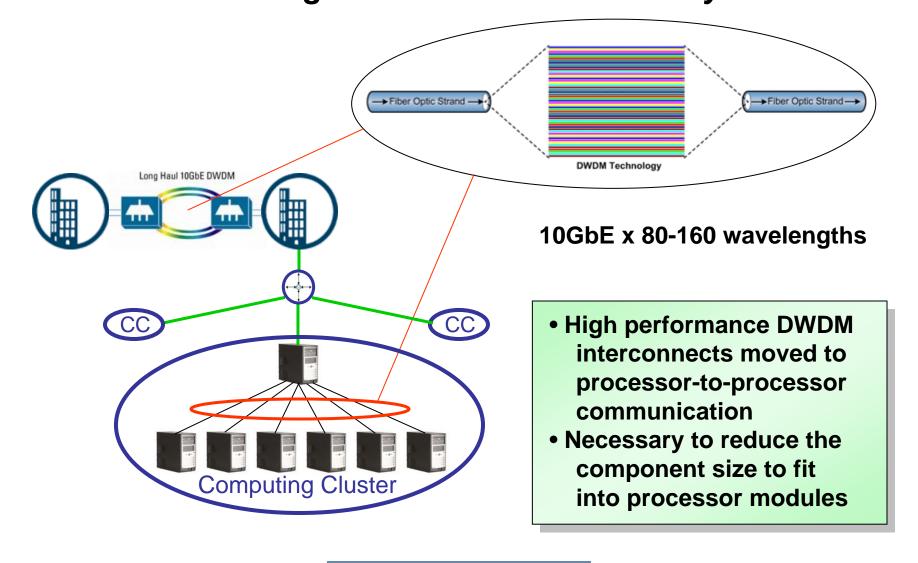

# Use of Dense Wavelength Division Multiplexing (DWDM) Optical Interconnects to Improve Processing Architecture Connectivity

## Air Force Research Laboratory Highly Integrated Photonics (HIP) Program

#### **Three Phase Program Overview**

|                      | Phase I                                           | Phase II                                   | Phase III                                            |

|----------------------|---------------------------------------------------|--------------------------------------------|------------------------------------------------------|

| Length               | 12 Months                                         | 33 Months                                  | 42 Months                                            |

| Scope                | Architecture Formulation/<br>Core Technology Demo | Functional Prototype<br>Devices            | System Application Development                       |

| # Tech.<br>Suppliers | 1                                                 | 2                                          | 4                                                    |

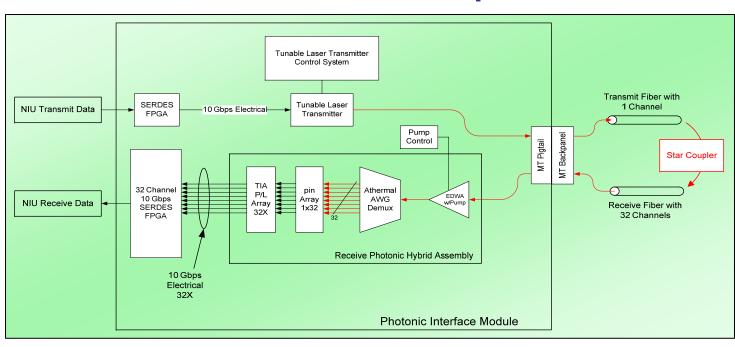

| Network              | Backbone & Bus:<br>Broadcast and Select           | Bidirectional Bus:<br>Broadcast and Select | WDM Star:<br>Broadcast and Select                    |

| Outcome              | Test Chips                                        | Functional Chips/<br>Lab Functional Demo   | Qualifiable Demonstration in Application Form Factor |

|                      | (CHIP A) OBIC                                     |                                            |                                                      |

## Air Force Research Laboratory Highly Integrated Photonics (HIP) Program

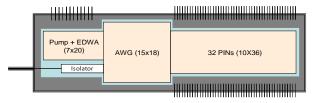

### **Phase III Component Overview**

- Optically transparent network

- Fault tolerant passive star

- Broadcast and select pushes packet routing to edges.

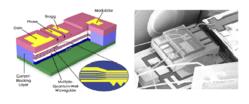

TEML schematic diagram: DBR laser + EA modulator SEM micrograph of a TEML chip fabricated at Multiplex