## DIFdoc: a standard format for visualizing hierarchical dataflow representations

Ivan Corretjer, University of Maryland Shuvra S. Bhattacharyya, University of Maryland

## High Performance Embedded DSP Design

- Dataflow has been shown to be a highly intuitive and efficient conceptual and visual format

- Formal properties (scheduling, bounded memory, etc.)

- Hierarchical (captures complex designs)

- Exposes parallelism

- Many commercial tools utilize dataflow for DSP system design, e.g. ...

- Gedae

- National Instruments LabVIEW

- Agilent ADS

## **DIFdoc**

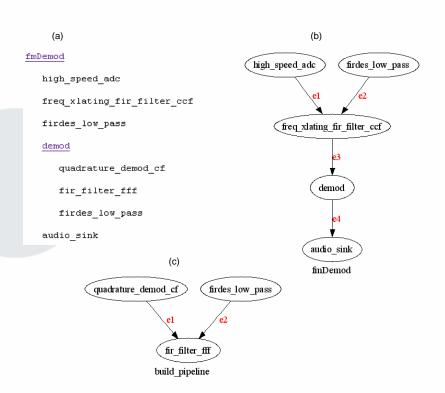

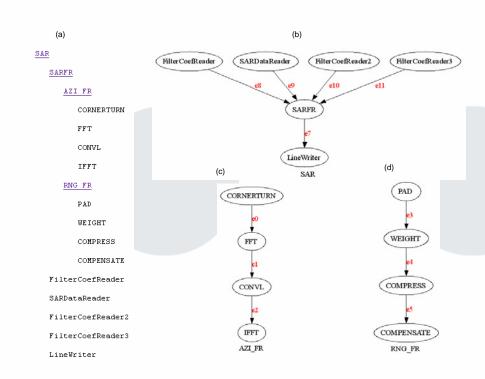

- Combined textual-pictorial representation of dataflow designs

- Provides a unique representation of an entire dataflow hierarchy

- Tool-independent

- Human-readable dataflow graph documentation format

- Displays dataflow-based design hierarchies using <u>HTML</u> and <u>dot</u>

- Indentation used to represent hierarchy

- Pictorially represent graphs

## **DIFdoc Examples**

FM demodulation example from GNU radio.

Synthetic aperture radar example from MCCI.