# What Makes HPEC Applications <u>Challenging?</u>

### **Understanding Application/Architecture Interactions**

David Koester, Ph.D. dkoester@mitre.org

21 September 2005

#### HPEC 2005 Poster Session

This work is sponsored by the Department of Defense under Army Contract W15P7T-05-C-D001. Opinions, interpretations, conclusions, and recommendations are those of the author and are not necessarily endorsed by the United States Government.

Slide-1 What Makes HPC Applications Challenging

© 2005 The MITRE Corporation. All rights reserved

MITRE

- It is critical for the HEC community to be able to articulate "What makes HPEC applications challenging?"

- The "challenging" part has a lot to do with the "High Performance" in HPEC

- Want to get the most out of the system

- Go after the biggest problems

- We must better articulate requirements to the HPEC vendor community to receive technologies that meet user needs

- HPEC vendor community

- HPEC research community

- "Application Challenges" create "bottlenecks"

- The performance of a system *"in series"* is obviously limited by the lowest performance component

- We need to apply the *"right amount"* of resources that provide the *"right"* improvement in the time to solution

- Where is performance lost when an application is run on an HPEC architecture?

- When does it make sense to invest in HPEC architecture to improve application performance?

MITRE

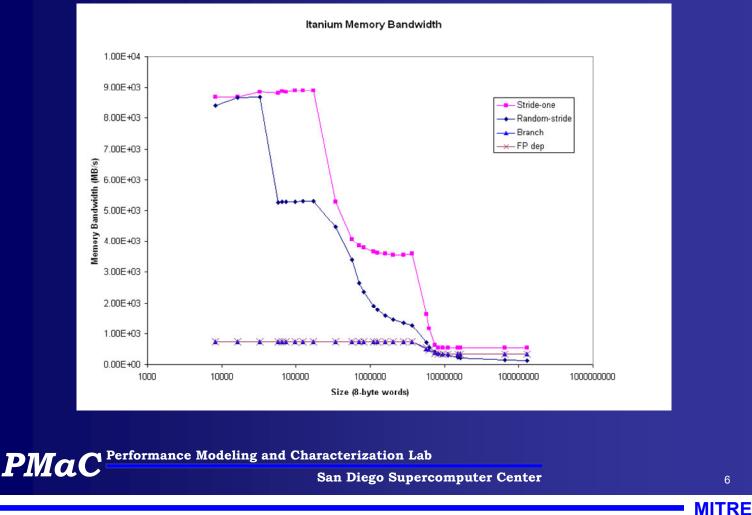

## Branch and Data Dependencies Intel Itanium MAPS Graph

#### Framework addition: Data Dependency

## Branch and Data Dependencies Intel Itanium MAPS Graph

- Many of the issues that make HPEC applications "challenging" are related to the memory wall and not to Moore's Law

- Minimizing the effects of the memory wall have consumed a large percentage of the transistors made available as the transistor density has increased

- Degraded performance is a result of disruptions in the computational pipeline — an incidence of currency within the microprocessor

- HPEC application programmers need to understand thoroughly the "challenges" in applications if there is any possibility for software to save Moore's Law