### Sustaining Moore's Law with A Super FPGA - Challenges and Solutions

Venkatesh Akella and Soheil Ghiasi

Department of Electrical & Computer Engineering

University of California

Davis, CA - 95616

{akella,ghiasi}@ucdavis.edu

# Computational Platform to Sustain Moore's Law In the Long Run

#### **KEY CRITERIA**

- Exploit Parallelism Sharing/Reuse not important

- Exploit Modularity No global clocks

- Avoid Centralized communication structures like register files, caches and memories and replace by scalable, user-programmable data forwarding networks

- High-level Language based tools

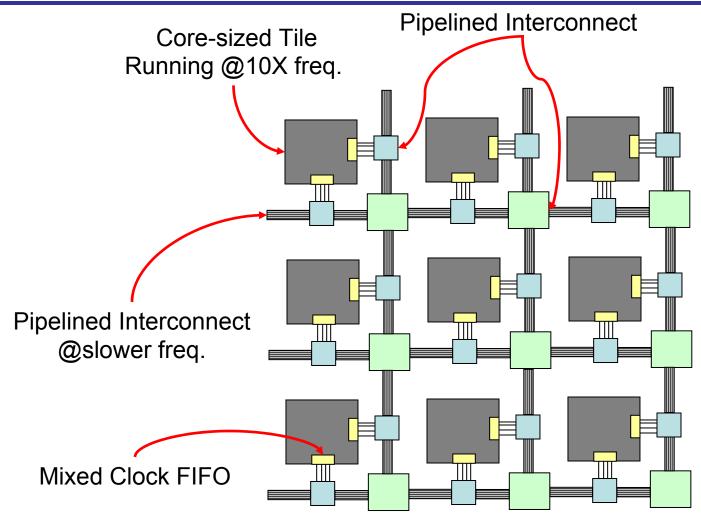

## Super FPGA - Derived from Synchroscalar

- Parallelism

- Reduced control overhead

- Statically configurable interconnect

- Frequency and voltage differentiation

University of California, Davis

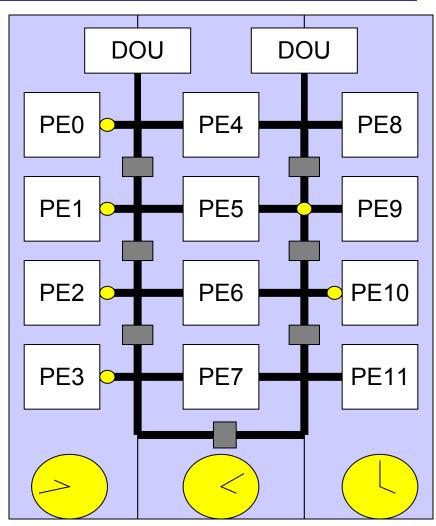

### Super-FPGA Architecture