# HPEC Related VITA Standards: An Update

Randy Banton

Mercury Computer Systems, Inc.

High Performance Embedded Computing (HPEC) Conference September 30, 2004

# **HPEC Related VITA Standards Activity**

- Switch Fabric Backplane

- VITA 41 "VXS" (VME Switch fabric Serial)

- VITA 46 "AMF" (Advanced Module Format)

- Switch Fabric Mezzanine

- VITA 42 "XMC" (Switch Fabric Mezzanine Card)

- Rugged Mechanical Infrastructure

- VITA 48 "ERDI" (Enhanced Ruggedized Design Implementation)

- Serial I/O

- VITA 17.2 "10Gb SFPDP"

- Digital Intermediate Frequency Interface

- VITA 49 "Digital IF"

VITA 41

"VXS"

(VME Switch Fabric Serial)

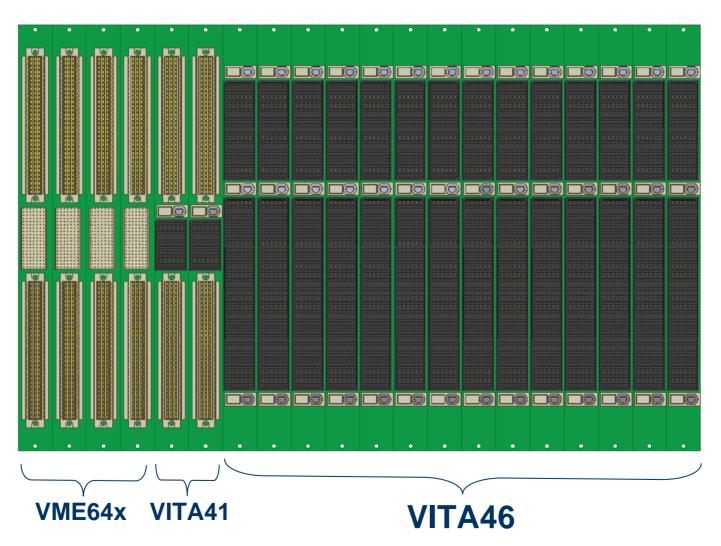

## VITA 41 & VITA 46

# Adding multi-gigabit serial interconnects to VME type infrastructures

- All approaches need new backplanes

- Existing connectors are not multi-gigabit capable

- All approaches can have some backwardcompatible VME slots

- VITA 41:

- Upgrade P0; Keep P1 & P2 DIN connectors

- Also define switch card with all new connectors

- VITA 46:

- Upgrade all connectors

- Also include current VME slots in backplanes

## **VITA 41 "VXS"**

Replace existing P0 with Multi-Gig RT2 7-Row

Add switch slots using all Multi-Gig RT2 9-Row

- - Backward compatibility with P1, P2 DIN connectors

- Downside

- Not compatible with boards using existing P0 2mm connector

- Limited number of high-speed pins in new P0 Multi-Gig connector

- Connectors not 2-level maintenance ready

- 3U format does not benefit from new P0 connector thus no allowance for high-speed signaling upgrades

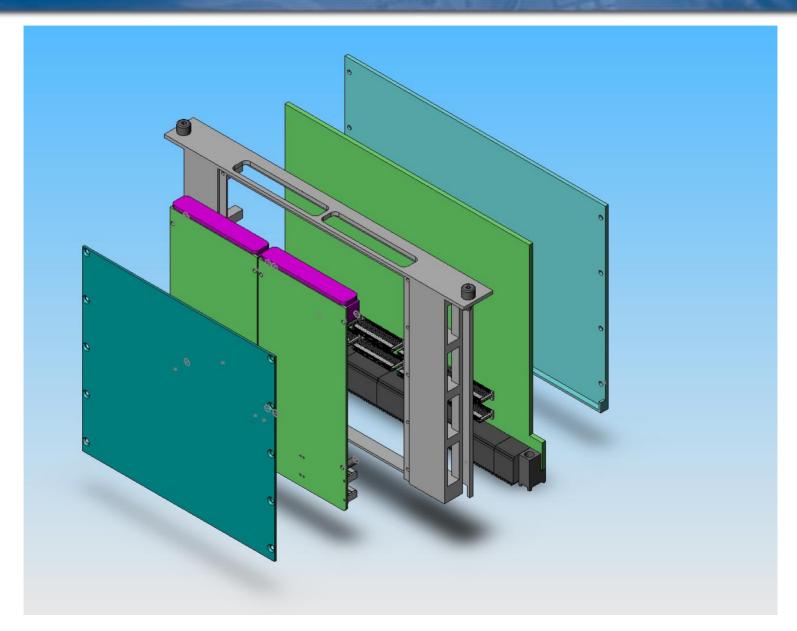

# VITA 41 Backplane

## **VITA 41 "VXS"**

## Status

#### VITA 41.0 base standard

Completed, drawings being updated

## - Protocol mappings

- VITA 41.1 Infiniband; completed

- VITA 41.2 Serial RapidIO<sup>®</sup>; completed

- VITA 41.3 Ethernet; in process

- VITA 41.4 PCI Express; in process

- VITA 41.11 RTM (Rear Transition Module); in process

VITA 46

"AMF"

(Advanced Module Format)

## VITA 46 "AMF"

Replace all connectors with Multi-Gig RT2 7-Row

### No switch card required

Enough pins are available to build large, rich topologies without one

#### Upside

- Enough high-speed pins (192 pairs) for switch fabric and large I/O counts

- Backward VME compatibility in some slots with VME on new connector

- Includes a 3U version, with high-speed serial I/O and fabric

- 2-level maintenance ESD ready connector system

#### Downside

- Not compatible with existing boards at slot level; No DINs for P1 & P2

- Backward VME compatibility in some slots with VME on new connector

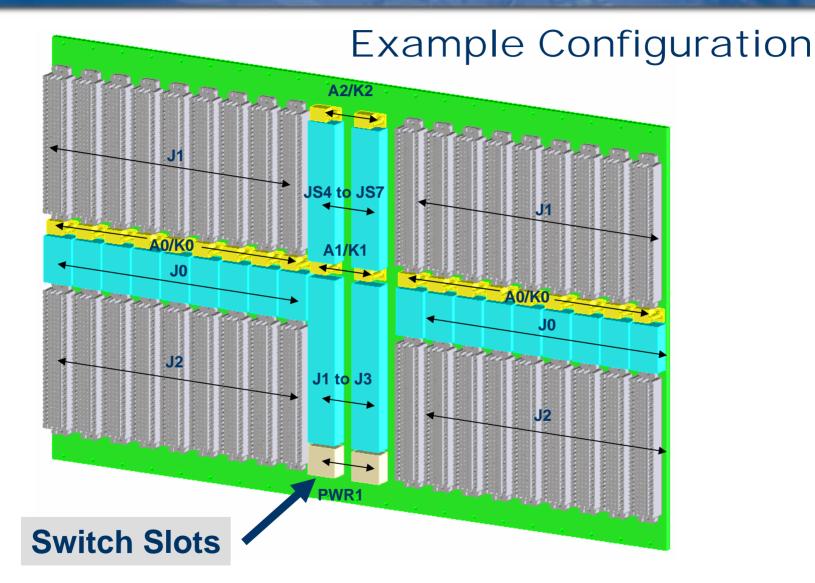

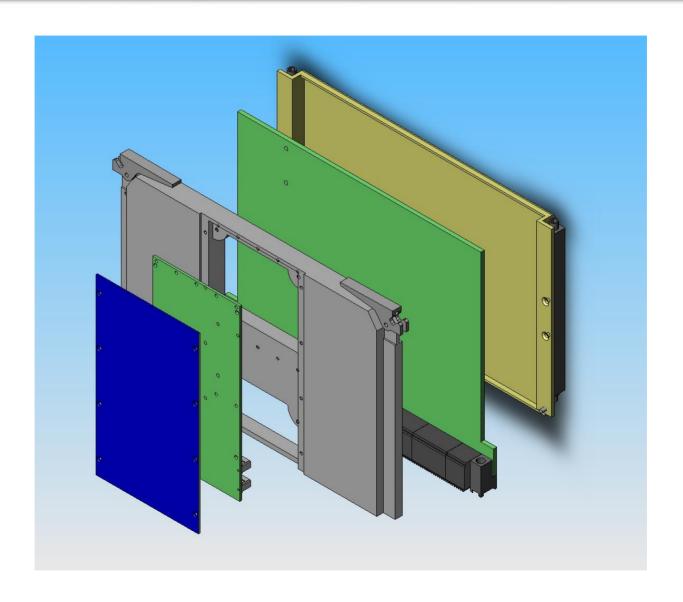

# Example VITA 46 Hetero- Backplane

## Heterogeneous Backplane for VME Legacy

## VITA 46 "AMF"

## Status

#### VITA 46.0 base standard

In process, draft in review

## Protocol mappings

- VITA 46.1 Parallel VME; in process

- VITA 46.2 Parallel cPCI; planned

- VITA 46.3 Serial RapidIO; planned

- VITA 46.4 PCI Express; planned

- VITA 46.5 HyperTransport<sup>™</sup>; planned

- VITA 46.x RTM (Rear Transition Module); planned

"XMC"

(Switch Fabric Mezzanine Card)

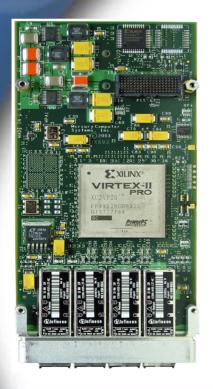

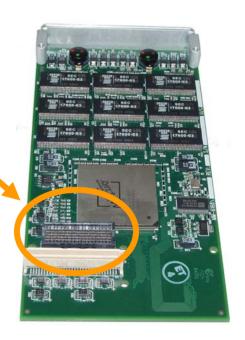

# VITA 42 "XMC"

- Began as RapidIO Trade Association "RMC"

- Transitioned to VITA for standardization

- Adds high-speed connector to existing CMC format

- Options for different protocols

- VITA 42.1 Parallel RapidIO

- VITA 42.2 Serial RapidIO

- VITA 42.3 PCI Express

- VITA 42.10 general purpose I/O

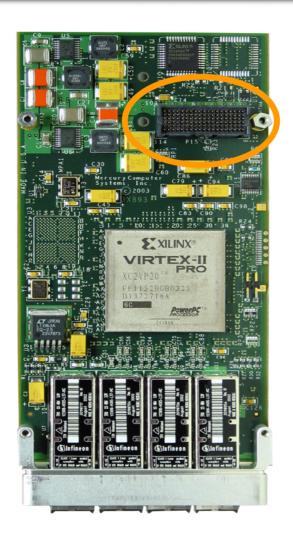

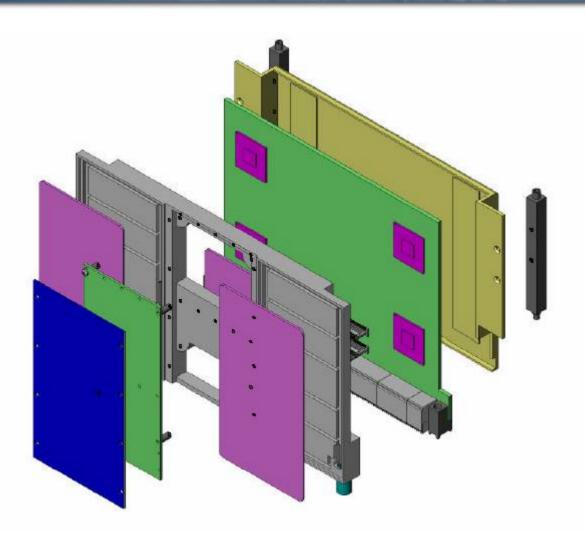

4 GB memory XMC with Parallel RapidlO

# **Example XMCs**

Interchassis XMC with Parallel RapidIO and 4 fiber I/O connectors running Serial RapidIO

Note – only 1 connector required for basic XMC. PMC connectors are optional.

## VITA 42 "XMC"

## Status

#### VITA 42.0 base standard

In process, final draft in review

## Protocol mappings

- VITA 42.1 Parallel RapidIO; in process

- VITA 42.2 Serial RapidIO; in process

- VITA 42.3 PCI Express; in process

- VITA 42.10 general purpose I/O; in process

## VITA 48

"ERDI"

(Enhanced Ruggedized Design Implementation)

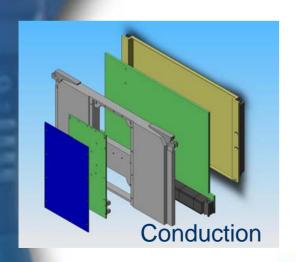

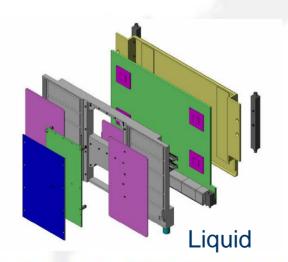

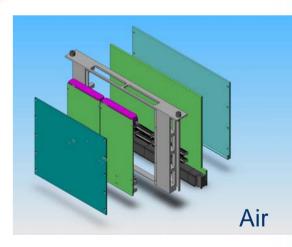

## VITA 48 "ERDI"

### As compared to present day IEEE1101.x standards ...

#### Board space & volume

- Space-saving methodologies possible

- New allocations of PWB thickness for high-density routing and power distribution, increased secondary-side components heights

#### Ruggedization

Improved methodologies for "out of the box" MIL-deployable ruggedization

#### Thermal management

- Unification of air-, conduction-, liquid-flow-thru-, and spray cooling methods

- Improve ability to thermally managed secondary side of PWB

- Allow for significant thermals planes in the PWB in addition to increased routing layers

#### Two-Level maintenance

- ESD protection at the board level in combination with other improvements

- Applies to all cooling methodologies

- ... and complementary to IEEE1101.x standards. There is no intent to "replace" these standards that still are useful in many other applications.

## VITA 48 "ERDI"

#### Commercial Market Driven Standards Not Sufficient

- Standards such as PICMG ATCA are pushing 40-50 CFM per slot for 150-200W power and 55C-like environments

- 10-20 CFM for military deployments tends to be the platform limit for air-cooling

- No commercial standards are pushing forward on non-aircooled methodologies

- 85C card cage desired for <u>conduction-cooled</u> solutions, 70C card edge often the lower acceptable limit

- MIL-deployable <u>liquid cooling</u> (e.g., liquid flow-thru) appears to becoming a technology and MIL-platform reality in next 3-5 years

- In general, new generation of commercial standards is not targeting the harsh shock, random vibration, endurance vibration, temperature, altitude, humidity, etc. of the HPEC MILdeployed world

# VITA 48 Air-Cooled Module

# VITA 48 Conduction-Cooled Module

# VITA 48 LFT Module

## VITA 48 "ERDI"

## Status

- VITA 48.0 base standard

- 。 In process, draft in review

## Connector system mappings

- VITA 48.1 VITA 46 connector system; in process

- VITA 48.2 VME64 connector system; planned

- ∘ VITA 48.3 cPCI connector system; ?

# Thank You!