### **Session 5: Standards Overview**

High Performance Embedded Computing (HPEC) Workshop 9:05 AM on September 30, 2004 for 2 hours, 20 minutes

Session Chair: Craig Lund CTO Mercury Computer Systems clund@mc.com +1 (978) 967 1264

### **Standards Triple Witching Hour**

- Hello commodity fabric

- Hello enhanced packaging

- Hello unique processor

- FPGA, GPU, game chip, etc.

## **Expectations**

- Computer users expect unrelenting Moore's Law improvements

- In 1965 Moore observed that the number of transistors fabricated per square inch doubled every 12 months

- Later revised to 18 months

- Moore said nothing about improved

- GigaFLOPS per dollar or watt or square inch

yet each is a metric that our community expects will follow Moore's Law

Gordon Moore

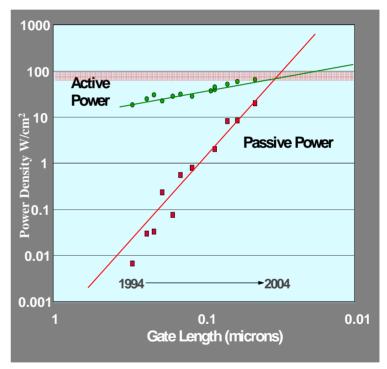

## Public Enemy #1

- Increasing "passive power"

- Has stalled the entire industry with respect to offering customers improved performance per watt.

- What is it?

- Current flows across regions

of semiconductor structure in

which no current should be

flowing.

IBM Microelectronics Graph

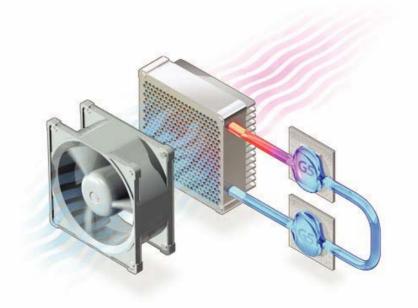

## **Example: Apple Liquid Cooling**

• On June 9th Apple announced a 2.5 GHz IBM 970 system that uses liquid cooling. Apple uses a high capacity variation of the heat pipes found in laptops.

#### **Heat Busters!**

- Mercury/VME Community: VITA 48

- Intel/PICMG: AdvancedTCA® and MicroTCA

- Intel/IBM: Open BladeCenter™

### **Infrastructure Talks**

- Prior HPEC years have featured VITA 42 (VXS) and ATCA.

- After the break, Mercury's Randy Banton will quickly overview all of VITA's infrastructure activities, including VITA 48.

- Pentek's Paul Mesibov will follow Randy to give more details on VITA 49, also known as DigitallF.

### **Architecture Drives Interconnect Standards**

The next three slides look backwards in time. They show that, as computer technology gets smaller, internal interconnect requirements evolve.

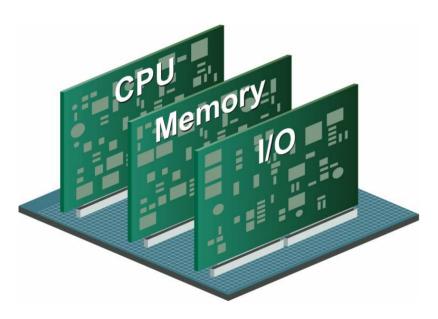

### **Architecture Circa 1980**

Computers contained multiple circuit boards connected by a shared bus.

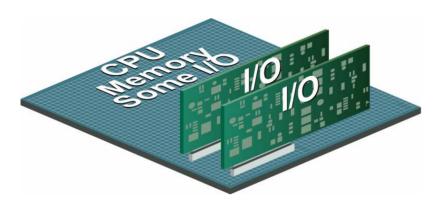

### **Architecture Circa 1990**

- When CPU and memory could fit onto a single card, the bus connection off the board became I/O oriented.

- PCI bus was first deployed around 1994 and quietly found its way into embedded devices

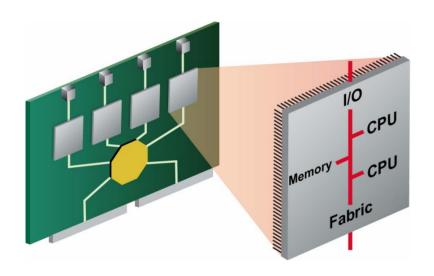

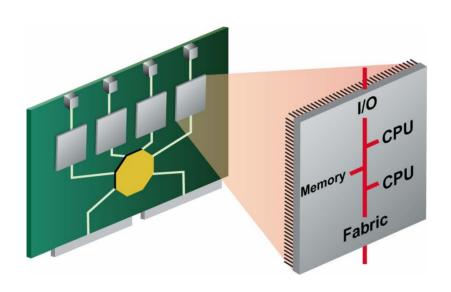

# **Architecture Today**

- System-on-a-chip (SOC) technology has evolved the basic architecture of an embedded system from master/slave toward peer-to-peer.

- Mercury pioneered this basic architecture within the embedded domain with ANSI/VITA RACEway in 1993. We joined with Motorola to develop what became RapidIO<sup>®</sup> in 2000.

### No Fabric Talks

- We have covered fabrics extensively in past HPEC workshops.

HPEC-oriented products are now shipping.

- I put the architecture slides into this summary for another reason . . .

## Software Standards Delayed

- Today's SOC architecture impacts the software model. Everything becomes a little multicomputer.

- Commercial OS and middleware vendors are responding with proprietary solutions that enable DMA transfers among the sea of peer SOC processors.

- So far users appear content to accept proprietary APIs provided the enabling software runs on hardware from multiple vendors.

## **Changing Focus**

- Past HPEC solutions targeted stand-off applications.

- Looking forward, HPEC solutions will move in-theater.

- The impact on software is to raise the importance of the intheater network. Think grid computing.

## Today's Software Advances in Adjacent Domains

- Thus today's software talks:

- RTI will discuss their publish/subscribe technology, standardized by OMG and recommended in the Navy Open Architecture.

- Verari (RackSaver plus MPI SoftTech) will discuss multiple vendor interoperability of MPI implementations.

# **Session Agenda**

| 9:05                                | 15 min | Standards Overview Craig Lund                                            |

|-------------------------------------|--------|--------------------------------------------------------------------------|

| 9:20                                | 25 min | GPUs: Engines for Future HPC (invited) Dr. John Owens of UC Davis        |

| 9:45                                | 25 min | OMG Data Distribution Service (DDS)  Mr. Gerardo Pardo-Castellote of RTI |

| 10:10                               | 25 min | High Productivity MPI Dr. Tony Skjellum of Verari Systems Software       |

| Break (view next session's posters) |        |                                                                          |

| 10:55                               | 15 min | HPEC Related VITA Standards: An Update Mr. Randy Banton of Mercury       |

| 11:10                               | 15 min | DigitallF Interface Standardization Mr. Paul Mesibov of Pentek           |

### **Invited GPU Talk**

- Some people are using GPUs today for computation. Few standards exist at this point. Nevertheless . . .

- The HPEC Program Committee

decided to invite an expert to give us a

broad introduction to this new

application of a technology that all of

us already have.

- I yield the podium to Dr. John Owens, an assistant professor at UC Davis.